B

POST checkpoint codes

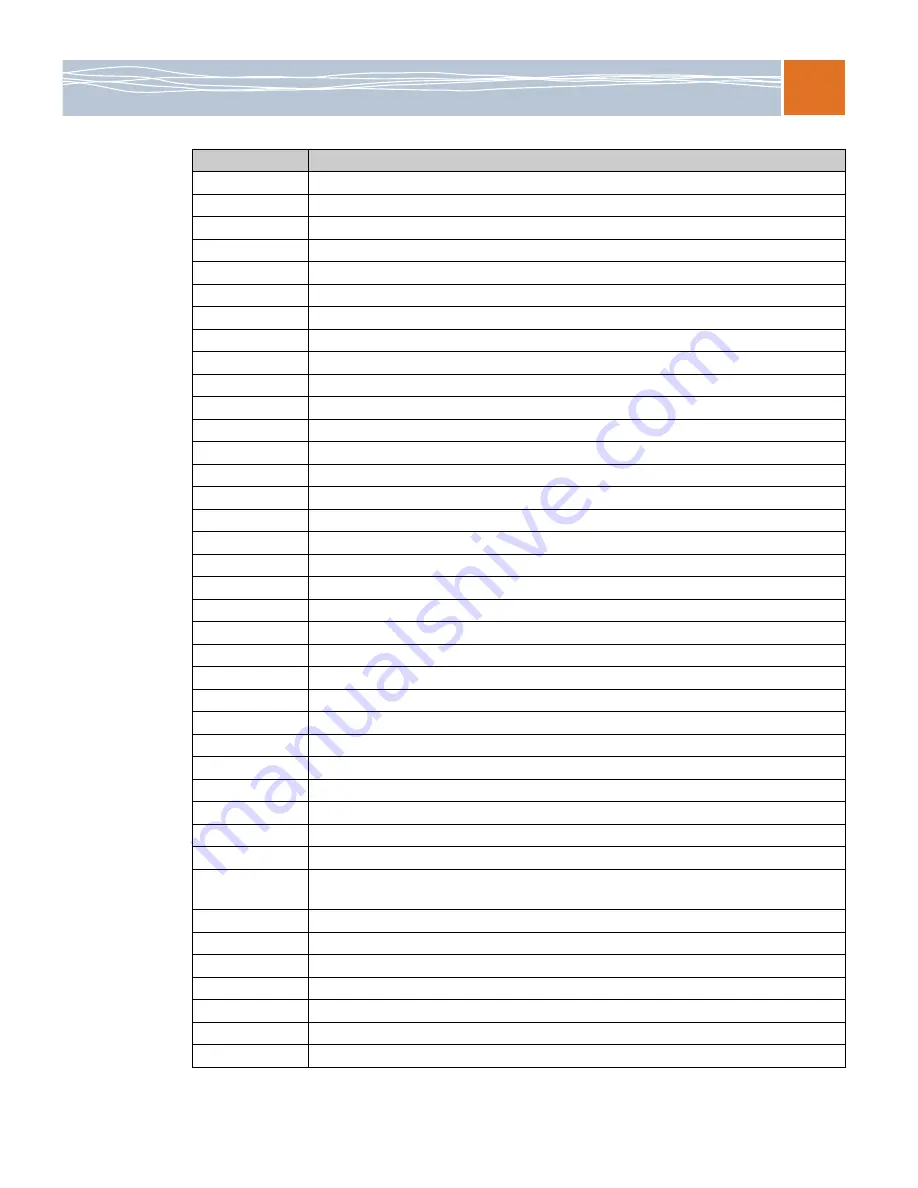

65

60h

Performs memory tests on extended RAM.

62h

Preforms address tests on extended RAM.

66h

Configures MTRR for extended memory caching.

67h

Initializes the non-primary processors.

68h

Enables cache(s).

69h

Initializes SMM, SMRAM and SMI code.

6Ah

Displays cache size.

6Ch

Displays BIOS shadow status.

6Eh

Zeroes un-initialized extended memory with cache on.

70h

Displays any errors found.

72h

Checks bad configuration.

76h

Reports if there was a Keyboard or Controller failures.

7Ch

Initializes hardware interrupt vectors.

7Eh

Coprocessor initialization.

81h

POST device initialization.

82h

Initializes RS232 devices.

83h

Configures non-MCD IDE controllers.

84h

Initializes parallel port(s).

85h

Configures PC Compatible Plug and Play ISA devices.

87h

Initializes MCDs (motherboard configurable devices).

88h

Initializes time-outs, key buffer, soft reset flag, and shadow RAM.

89h

Enables NMIs.

8Ah

Initializes extended BIOS data area.

8Bh

Sets up PS/2 mouse interrupt & initialize extended BDA.

8Ch

Initializes legacy floppy disk drive(s).

90h

Tests hard disks.

91h

Programs timing registers according to PIO modes.

93h

Creates MP tables.

95h

Tests CDROM.

96h

Exits big real mode.

97h

Fixes up the MP table physical pointer and checksum.

98h

Configures non-PC-compatible Plug and Play ISA devices, PCI IRQs, enable PCI devices and

ROM-scan.

99h

Checks SMART status.

9Ch

Late SMM (system memory mode) initialization.

9Dh

Initializes the system security engine.

9Eh

Enables the proper hardware interrupts.

A0h

Sets time of day.

A2h

Tests if key lock or keyboard controller password is on.

A8h

Removes the “Press F2 for Setup“prompt.

Checkpoint Code Description

Summary of Contents for PL35Q

Page 6: ...6 ...

Page 8: ...8 ...

Page 20: ...2 Product Specification 20 ...

Page 38: ...3 Hardware Reference 38 ...

Page 58: ...A Connector Description 58 ...

Page 72: ...C 72 ...