Chapter 4: Theory of Operation

41

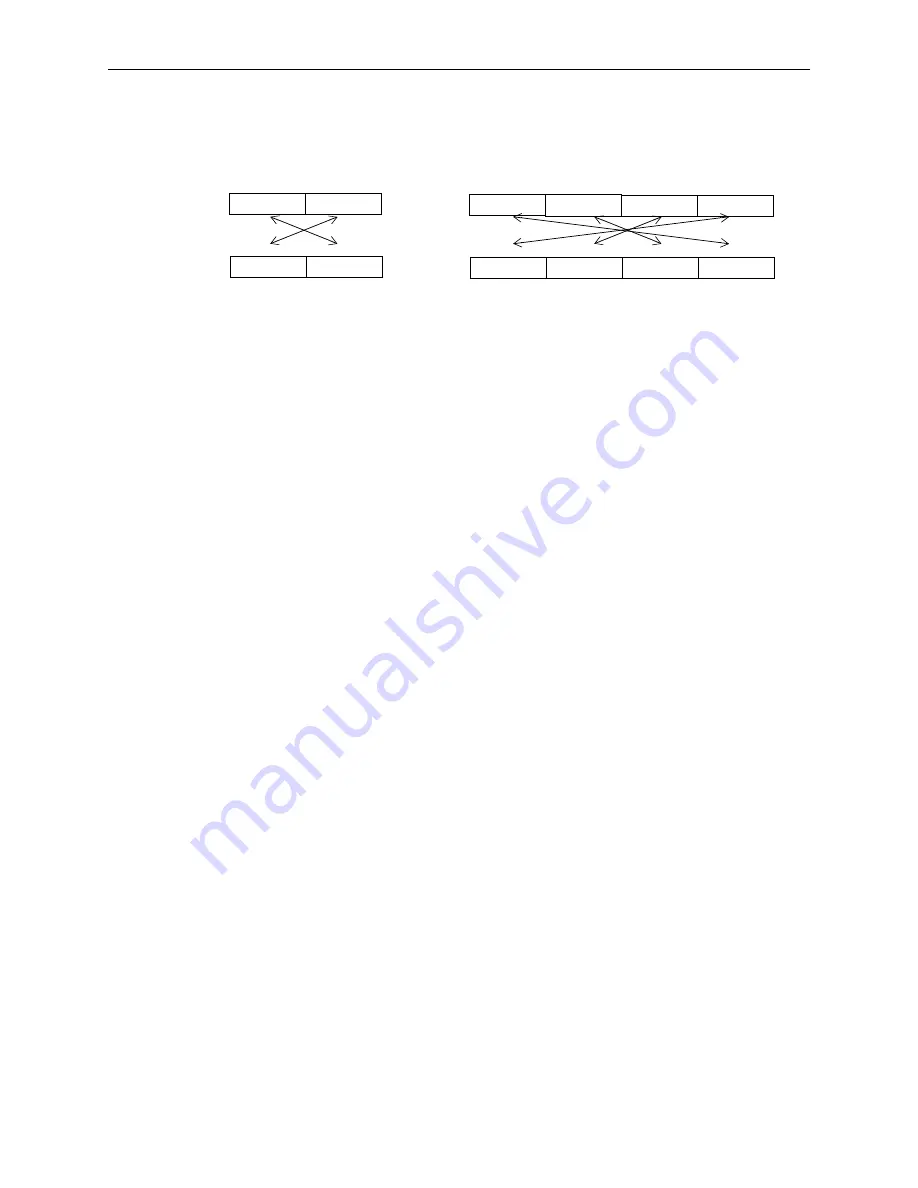

When big-endian is selected, the bytes are swapped between the 486 and VME as shown

in the next diagram.

When using big-endian byte ordering, care must be taken to assure that the VME address

is aligned on a boundary; for D16 accesses the VME address must be on a word boundary

(address evenly divisible by 2) and for D32 accesses the VME address must be on a

double-word boundary (evenly divisible by 4). If this is not done, the results are

“scrambled” data. Although the VMEbus address must be boundary-aligned to match the

data width (word or double-word), the 486 address does not need to be boundary-aligned.

Another consideration is the compiler being used. Some compilers produce two 16-bit

accesses when a 32-bit access is desired. When this occurs, again the data is “scrambled.”

When transferring a 32-bit floating-point number, special care must be taken to assure that

both processors use the same floating-point format; that both systems expect the mantissa

and exponent in the same byte locations. As long as this is correct, transferring a

floating-point number works correctly. Since transferring a 64-bit floating-point number is

not supported in hardware, two 32-bit transfers must be used with little-endian byte order

and then byte-swapping must be accomplished in software.

The EPConnect Bus Manager software provides a means of selecting the byte ordering

during memory-copy operations.

VMEbus Interrupt Response

When the EPC-8A’s Interrupt Generator register (815Fh) is used to assert an interrupt, the

EPC-8A formulates a status/ID value that is transmitted on the bus as the response to a

matching interrupt acknowledgment cycle. The EPC-8A acts as both a D08(O) and D16

interrupter. For D08 interrupt acknowledge cycles, the status/ID value is the EPC-8A’s

logical address (

11111aaa

, where

aaa

is the value of ULA as defined in port 814Ah). For

D16 and D32 interrupt acknowledge cycles, the status/ID value consists of 16 bits. The

upper eight bits are the upper half of the response register (the value in I/O port 814Bh)

and the lower eight bits are the logical address.

VME Extension Registers (VXI)

EPC-8A maps a standard set of VXI configuration registers onto the VMEbus A16 space

and thus accessible by other VMEbus modules. These registers are 16-bit registers

occupying 64 bytes of A16 space at a base address defined by the EPC-8A’s logical

address. The VME-mapped registers are a subset of those defined as I/O ports in the

EPC-8A. The registers are dual-ported in that they are accessible both from VME and

from within the EPC-8A as ports in its I/O space.

Refer to Appendix F, VMEbus Mapped Registers for additional information.

Figure 4-4. Using big-endian byte ordering

76

54

32

10

486

Address

Addr+3

Addr+2

Addr+1

Addr

76

54

32

10

Motorola

Address

Addr+3

Addr+2

Addr+1

Addr

LSB

MSB

32

10

Addr+1

Addr

10

32

Addr+1

Addr

LSB

MSB

D16 access

D32 access

Summary of Contents for EPC-8A

Page 38: ...EPC 8A Hardware Reference 28 ...

Page 68: ...EPC 8A Hardware Reference 58 ...

Page 72: ...EPC 8A Hardware Reference 62 ...

Page 74: ...EPC 8A Hardware Reference 64 ...

Page 82: ...EPC 8A Hardware Reference 72 ...

Page 94: ...EPC 8A Hardware Reference 84 ...

Page 108: ...EPC 8A Hardware Reference 98 ...

Page 118: ...EPC 8A Hardware Reference 108 ...