DVR-230-S

82

1

2

4

1

2

3

4

C

D

F

A

B

E

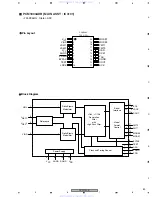

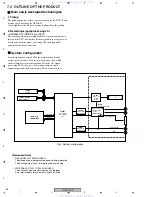

• 1 Chip System Codec

UPD61181F1-105MN2A (MAIN ASSY : IC1001)

(EMMA2RL)

Block Diagram

1394 Link

DV decode

Peripheral

Audio

Processor

CSS/CPRM etc.

Video

Decoder

Video

Encoder

Display

Controller

&

Scaler

Unified

Memory

Controller

Ext. Memory

DDR33

CPU

MIPS32

MPEG

AV

Encode

CPU

MIPS32

MPEG

Video

Decode

AV

Switch

1st

ATA

2nd

ATA

Stream

Processor

BT.656 or

BT.1358

CVBS or Y/C

DV

MPEG-TS

PCM

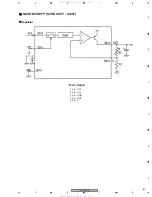

Video siganl

Input block

Color

demodulation

Clock generator

VBI

detection

Video signal

output block

I2C register

Video signal

output

Y/C separation

processing

block

Clock

Conversion

processing

block

Video signal

input

S/PDIF

480P

480I

BT.656

Stream

DVD

HDD

[Each Block]

1. MAIN CPU

CPU of 187MHz, 32bit, MIPS32

Attached with EJTAG debugger interface

8. MPEG AV Encoder

Video : MPEG1, 2

Audio : MPEG1, 2 Conversion to LPCM

2. Sub CPU

CPU of MIPS32

Operating for DSP section

9. Stream processor

Interface of stream

Decription of CSS, CPRM

En/Decription of CPRM, DES

10. MPEG Decoder

Video : MPEG1, 2, JPEG

This decoder is able to decode 2 signals simultaneously.

Audio : MPEG1, 2, LPCM, MP3, WMA, Dolby-digital

Test tone, Virtual surround

5.1ch Dolby-digital(option)

11. Video Encoder

Video DAC of 554MHz/10 bit

Correspond to 5ch Y, Pb, Pr(RGB, Component), YC(CVBS) of

NTSC/PAL/SECAM

3. Memory Controller

Correspond to DDR

×

2 of 128Mbit – 512Mbit

Frequency is up to PC333(166MHz

×

2)

Universal input/output interface

Communication with TUFL-con

Watch-dog timer

VDEC of 240MHz/10bit

Input is only YC 2ch, or V.

3D Y/C separation, 3D noise filter

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299