4-1

4-1

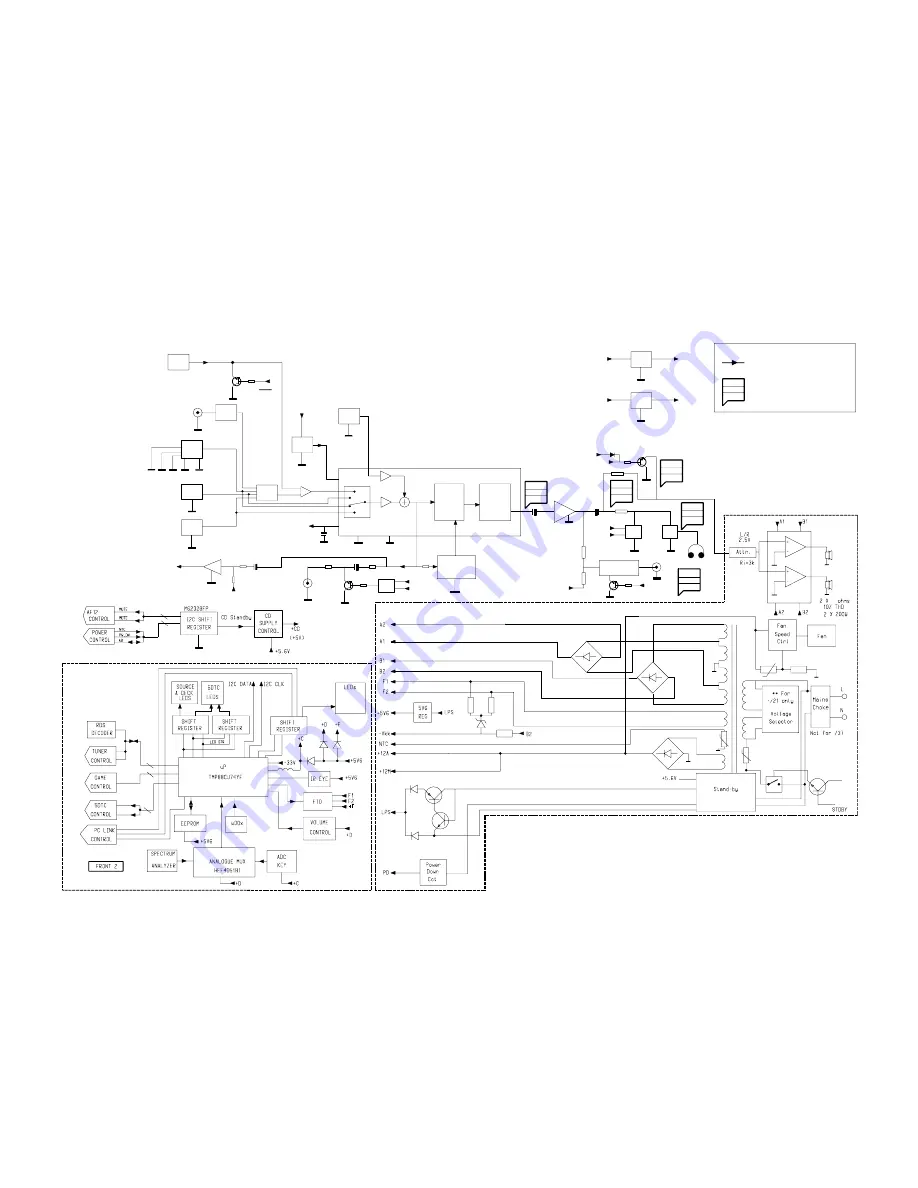

SET BLOCK DIAGRAM

-8.5 dB

HEF

4052

GAME

PORT

YY dBA

ZZ dB

D

78dBA

250mV

SIS Filter

Chan.

A

XX mV

SUBWOOFER

CCT

A

Attn

A

MAIN SIGNAL PATH

MEASUREMENTS ARE IN AUX MODE :

125mV

H/P

DPL/

Mute_SW_FR

From other

Chan.

FIS or

A

(Blue Strip)

(wOOx)

(BassTreble)

NOTE :

H/P

3.2dB

0.8V

86dBA

3.5dBA

A

S/W OUT

CCT

CCT

LOW_PW_SPLY

A

Signal

S/N AT 500mW

HEADROOM (1% THD) WRT TO LEVEL AT MAX VOL

500mV

SA_OUT

-Vkk

+9V1

A

Mute2

-Vkk

TUNER

IS

Interface

Audio

Mute

-CMOS

A

A

D

A

-9V

+5V

From other

5DTC

Mute1

LEVELS AT MAX VOL

D

REG.

+12V_A

-CMOS

Proc.

Mute_SW_FR

H/P Amp

2.50V

85dBA

3dB

AUX 640mV

A

A

VREF

CON

200mV

76dBA

16dB

1.90V

67dBA

3dB

Mute

A

REG.

+5V6

-VKK

2.1V

Mute_SW

A

MIC

A

DIG

Line Out

A

A

125mV

Game

A

GAME 310mV

650mV

A

PC-LINK

A

A

D

REG.

CCT

M

Supply

-ECO

8

UCD

LPS

Summary of Contents for FW-M589

Page 16: ...Service position A Service position B Service position C 2 4 2 4 DISMANTLING INSTRUCTIONS ...

Page 62: ...9 2 9 2 AF12 BOARD COMPONENT LAYOUT ...

Page 63: ...9 3 9 3 AF12 BOARD CHIP LAYOUT MAPPING AF12 BOARD COMPONENT LAYOUT MAPPING ...

Page 64: ...9 4 9 4 AF12 BOARD CHIP LAYOUT ...

Page 76: ...10 8 Location of switches ...

Page 84: ...10 16 10 16 Exploded view 5DTC mechanic for orientation only ...