137

Chapter 9

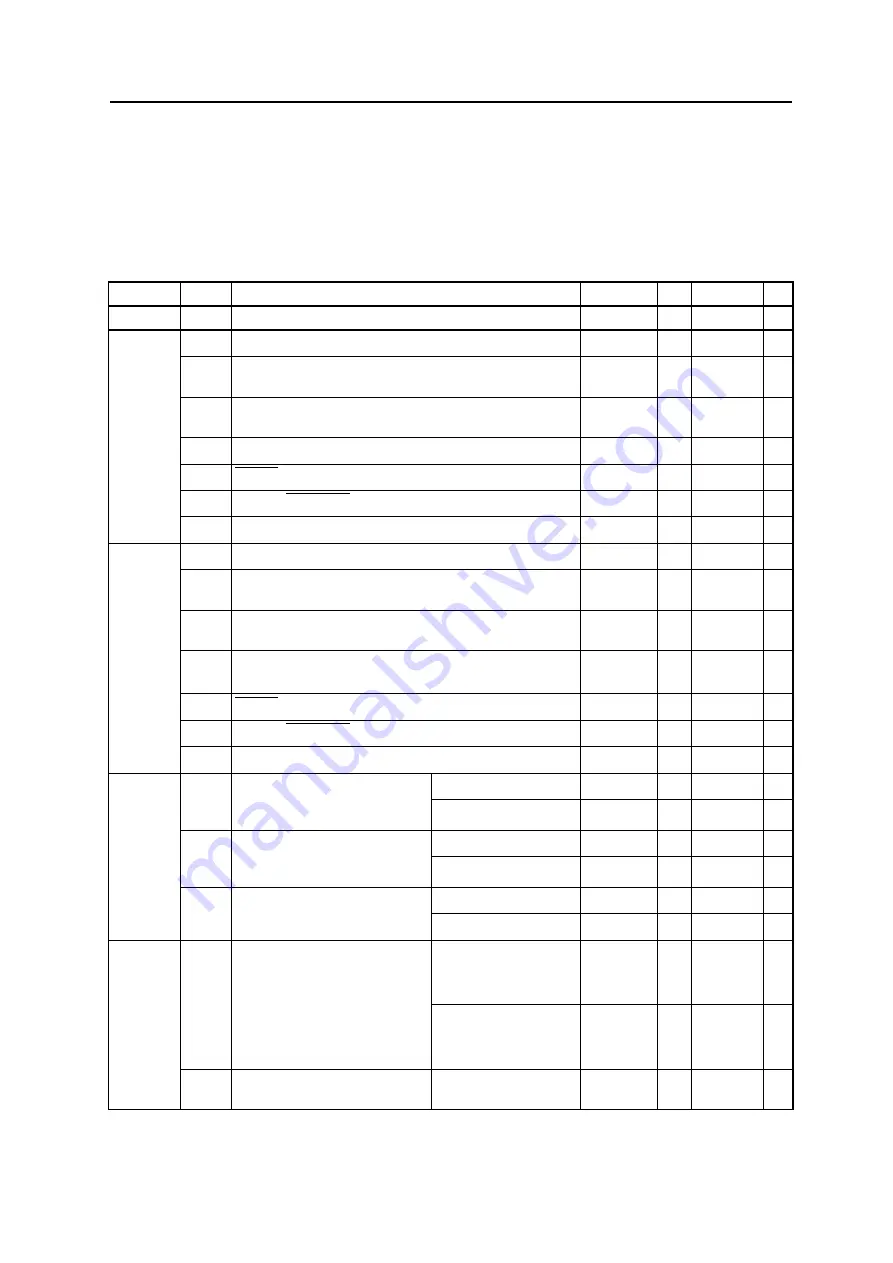

Electrical Specification

Preliminary User’s Manual U17763EE1V1UD00

9.6 DC

Characteristics

9.6.1 Input/Output

Level

(V

DD

=EV

DD

=BV

DD

=MTV

DD

=SMV

DD

=AV

REF0

=4.0 to 5.5 V,

V

SS

=EV

SS

=BV

SS

=MTV

SS

=SMV

SS

=AV

SS

=0 V,

T

A

=-40 to +85°C)

Parameter Symbol

Conditions

MIN.

TYP

MAX.

Unit

Input

voltage,

high

V

IH1

P30, P34, P36-P38, P41, P911

0.7 EV

DD

EV

DD

V

V

IH2

P00-P06, P10-P11, P31-P33, P35, P39, P40, P42,

P50-P55, P90-P96, P910, P912-P915

0.8 EV

DD

EV

DD

V

V

IH3

PCM2-PCM3, PCS0-PCS1, PCT0, PCT1, PCT4, PCT6,

PDL0-PDL13

0.7 BV

DD

BV

DD

V

V

IH4

P70-P715

0.7 AV

REF0

AV

REF0

V

V

IH5

RESET, FLMD0

0.8 EV

DD

EV

DD

V

V

IH6

PMT40, MTRESET

0.8 MTV

DD

MTV

DD

V

V

IH

7

PMT00-PMT03, PMT30-PMT35, PMT41-PMT43

0.7 MTV

DD

MTV

DD

V

Input

voltage,

low

V

IL1

P30, P34, P36-P38, P41, P98, P911

EV

SS

0.3 EV

DD

V

V

IL2

P00-P06, P10-P11, P31-P33, P35, P39, P40, P42,

P50-P55, P90-P96, P910, P912-P915

EV

SS

0.2 EV

DD

V

V

IL3

PCM2-PCM3, PCS0-PCS1, PCT0, PCT1, PCT4, PCT6,

PDL0-PDL13

BV

SS

0.3 BV

DD

V

V

IL4

P70-P715

AV

SS

0.3

AV

REF0

V

V

IL5

RESET, FLMD0

EV

SS

0.2 EV

DD

V

V

IL6

PMT40, MTRESET

MTV

SS

0.2 MTV

DD

V

V

IL7

PMT00-PMT03, PMT30-PMT35, PMT41-PMT43

MTV

SS

0.3 MTV

DD

V

Output

voltage,

high

V

OH1

a

P00-P06, P10-P11, P30-P39,

P40-P42, P50-P55, P90-P96,

P910-P915

I

OH

=-1.0 mA

EV

DD

-1.0

EV

DD

V

I

OH

=-100 µA

EV

DD

-0.5

EV

DD

V

V

OH2

PCM0-PCM3, PCS0-PCS1,

PCT0, PCT1, PCT4, PCT6,

PDL0-PDL13

I

OH

=-1.0 mA

BV

DD

-1.0

BV

DD

V

I

OH

=-100 µA

BV

DD

-0.5

BV

DD

V

V

OH3

b

P70-P715

I

OH

=-1.0 mA

AV

REF0

-1.0

AV

REF0

V

I

OH

=-100 µA

AV

REF0

-0.5

AV

REF0

V

Output

voltage,

high

V

OH4

c

PMT10-PMT17, PMT20-PMT27,

SM11-SM14, SM21-SM24

I

OH

=-27 mA (T

A

=85°C)

I

OH

=-30 mA (T

A

=25°C)

I

OH

=-40 mA (T

A

=-40°C)

SMV

DD

-

0.07

SMV

DD

-

0.7

V

I

OH

=-19 mA (T

A

=85°C)

I

OH

=-21 mA (T

A

=25°C)

I

OH

=-28 mA (T

A

=-40°C)

SMV

DD

-0.5

SMV

DD

-

0.7

V

V

OH5

d

PMT00-PMT03, PMT30-PMT35,

PMT40-PMT43

I

OH

=-1.0 mA

MTV

DD

-1.0

MTV

DD

V

Summary of Contents for V850ES/DJ2

Page 2: ...2 User s Manual U17763EE1V1UD00 ...

Page 8: ...8 User s Manual U17763EE1V1UD00 ...

Page 12: ...12 User s Manual U17763EE1V0UD00 ...

Page 16: ...16 User s Manual U17763EE1V0UD00 ...

Page 24: ...24 User s Manual U17763EE1V1UD00 MEMO ...

Page 103: ...103 Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 113: ...113 Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 127: ...127 Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 151: ...151 Chapter 9 Electrical Specification Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 153: ...153 Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 155: ...155 Preliminary User s Manual U17763EE1V1UD00 MEMO ...

Page 156: ...156 Chapter 11 Recommended Soldering Conditions Preliminary User s Manual U17763EE1V1UD00 ...

Page 160: ......

Page 161: ......