© National Instruments

|

4-23

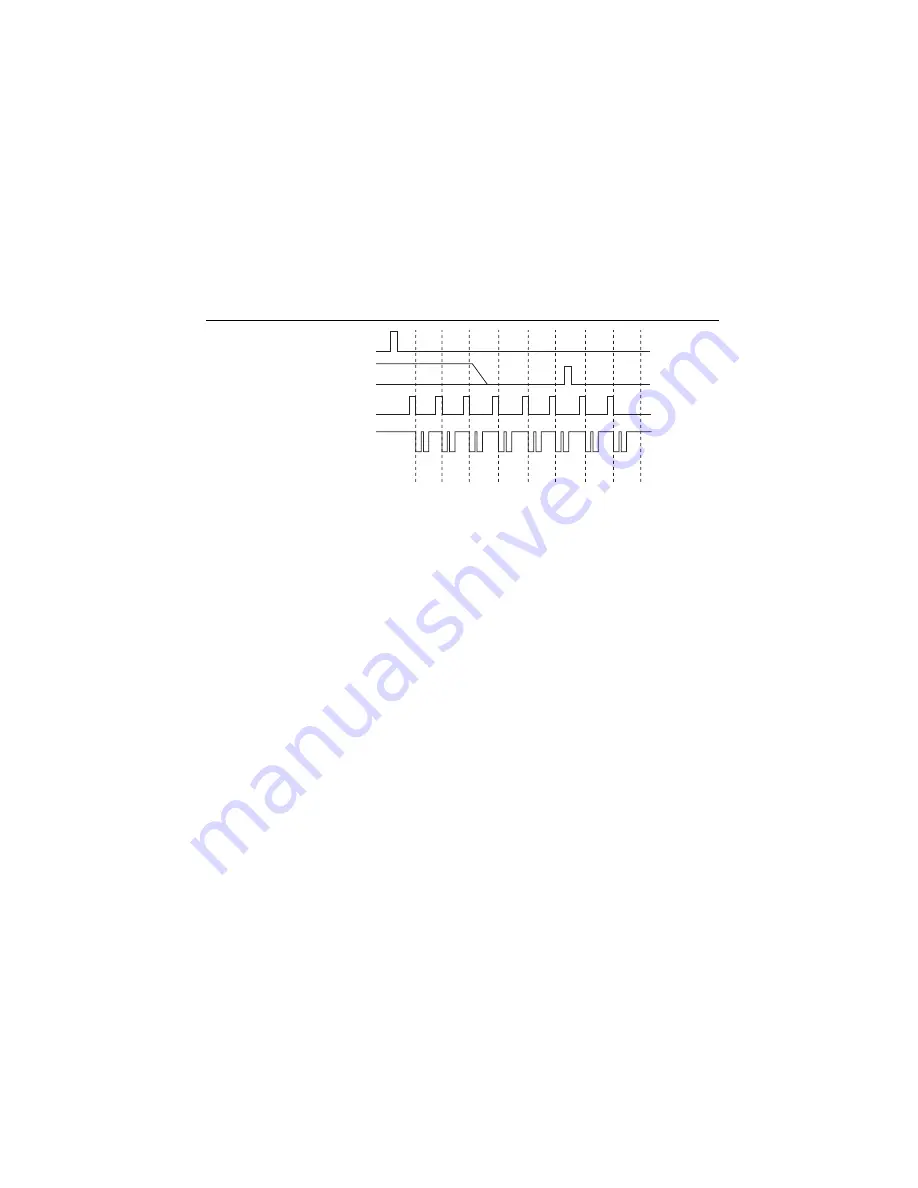

AI Start Trigger is set up to be a software start trigger, an output pulse appears on the

ai/StartTrigger line when the acquisition begins. When the AI Start Trigger pulse occurs, the

sample counter is loaded with the number of pretriggered samples, in this example, four. The

value decrements with each pulse on AI Sample Clock. The sample counter is then loaded with

the number of posttriggered samples, in this example, three.

Figure 4-15.

Pretriggered Data Acquisition Example

If an AI Reference Trigger (ai/ReferenceTrigger) pulse occurs before the specified number of

pretrigger samples are acquired, the trigger pulse is ignored. Otherwise, when the AI Reference

Trigger pulse occurs, the sample counter value decrements until the specified number of

posttrigger samples have been acquired.

M Series devices feature the following analog input timing signals:

•

•

AI Sample Clock Timebase Signal

•

•

AI Convert Clock Timebase Signal

•

•

•

•

AI Sample Clock Signal

Use the AI Sample Clock (ai/SampleClock) signal to initiate a set of measurements. Your

M Series device samples the AI signals of every channel in the task once for every AI Sample

Clock. A measurement acquisition consists of one or more samples.

You can specify an internal or external source for AI Sample Clock. You also can specify

whether the measurement sample begins on the rising edge or falling edge of AI Sample Clock.

n/

a

0

1

2

3

1

0

2

2

2

AI

S

t

a

rt Trigger

AI Reference Trigger

AI

Sa

mple Clock

AI Convert Clock

S

c

a

n Co

u

nter

Summary of Contents for PCI-6281

Page 1: ...PCI 6281...