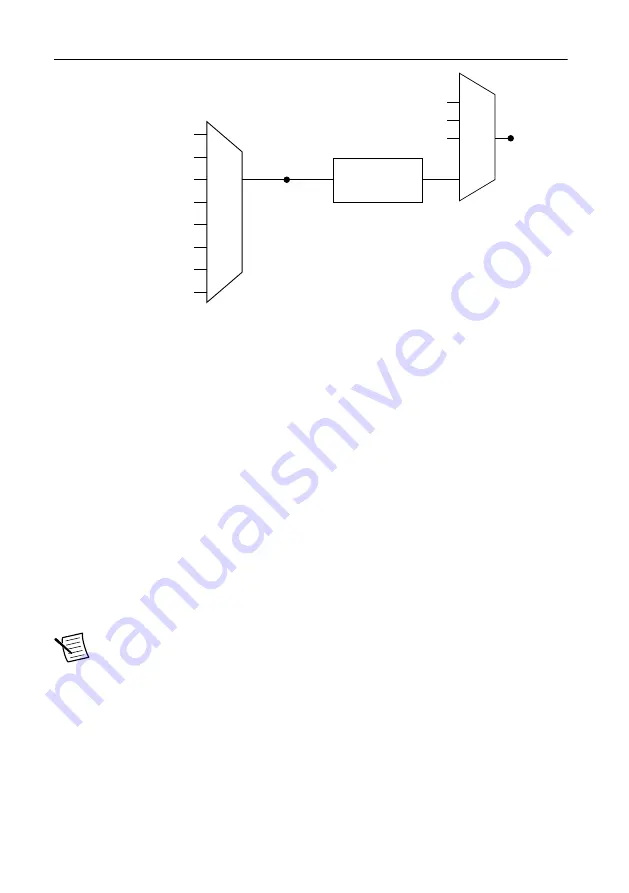

Figure 36. Analog Output Timing Options

Programmable

Clock

Divider

AO Sample Clock

Timebase

PFI

Analog Comparison Event

Ctr n Internal Output

Sample

Clock

Analog Comparison

Event

80 MHz Timebase

20 MHz Timebase

PFI

13.1072 MHz Timebase

12.8 MHz Timebase

10 MHz Timebase

100 kHz Timebase

Routing AO Sample Clock to an Output Terminal

You can route AO Sample Clock to any output PFI terminal. AO Sample Clock is active high

by default.

AO Sample Clock Timebase Signal

The AO Sample Clock Timebase signal is divided down to provide a source for AO Sample

Clock. AO Sample Clock Timebase can be generated from external or internal sources, and is

not available as an output from the controller.

Delta-Sigma Modules

The oversample clock is used as the AO Sample Clock Timebase. The cRIO controller

supplies 10 MHz, 12.8 MHz, and 13.1072 MHz timebases. When delta-sigma modules with

different oversample clock frequencies are used in an analog output task, the AO Sample

Clock Timebase can use any of the available frequencies; by default, the fastest available is

used. The update rate of all modules in the task is an integer divisor of the frequency of the

AO Sample Clock Timebase.

Note

DSA modules do not support HWTSP mode.

AO Start Trigger Signal

Use the AO Start Trigger signal to initiate a waveform generation. If you do not use triggers,

you can begin a generation with a software command. If you are using an internal sample

clock, you can specify a delay from the start trigger to the first sample. For more information,

refer to the

NI-DAQmx Help

.

cRIO-904x User Manual

|

© National Instruments

|

57