5-28

|

ni.com

Chapter 5

Counters

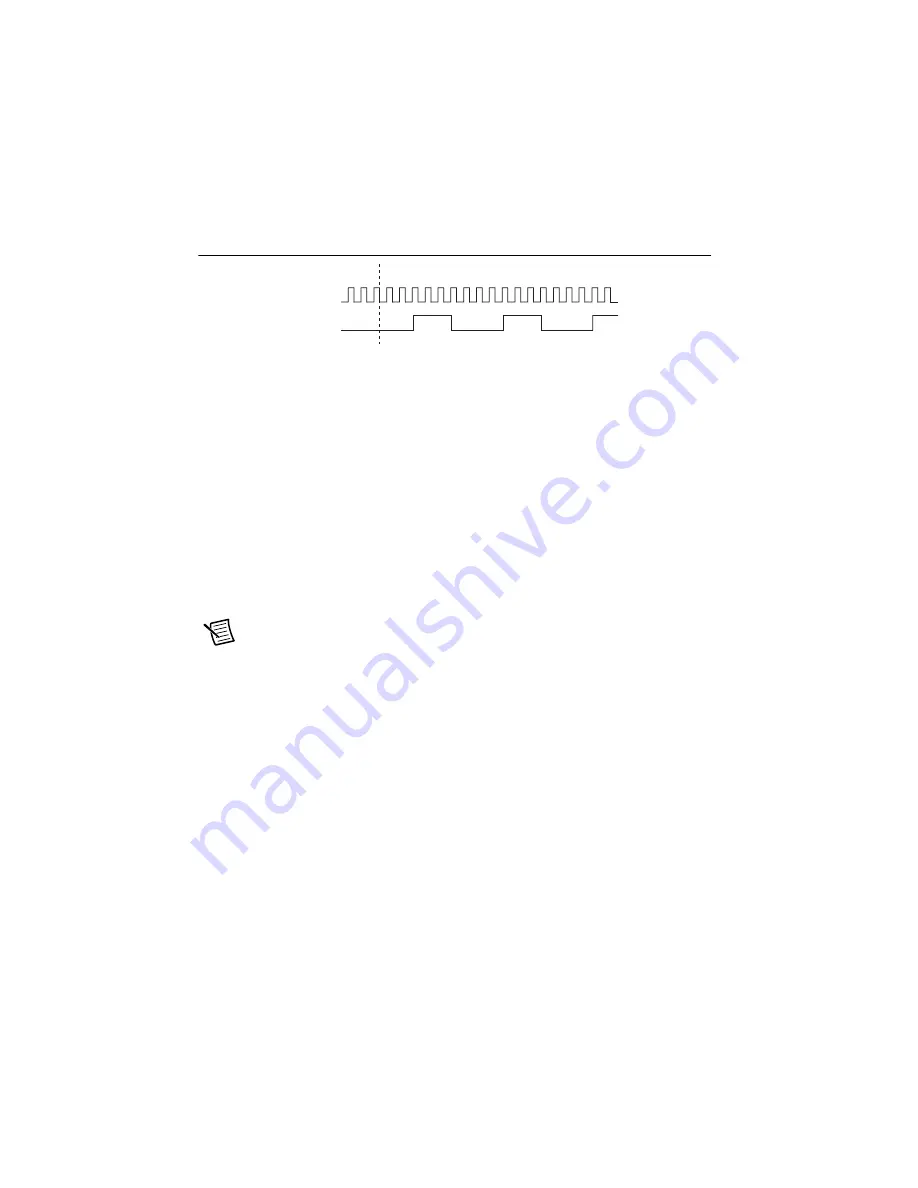

Figure 5-31 shows a continuous pulse train generation (using the rising edge of Source).

Figure 5-31.

Continuous Pulse Train Generation

Continuous pulse train generation is sometimes called frequency division. If the high and low

pulse widths of the output signal are

M

and

N

periods, then the frequency of the Counter

n

Internal Output signal is equal to the frequency of the Source input divided by

M

+

N

.

For information about connecting counter signals, refer to the

section.

Buffered Pulse Train Generation

The cDAQ controller counters can use the FIFO to perform a buffered pulse train generation.

This pulse train can use implicit timing or sample clock timing. When using implicit timing, the

pulse idle time and active time changes with each sample you write. With sample clocked

timing, each sample you write updates the idle time and active time of your generation on each

sample clock edge. Idle time and active time can also be defined in terms of frequency and duty

cycle or idle ticks and active ticks.

Note

On buffered implicit pulse trains the pulse specifications in the DAQmx

Create Counter Output Channel are ignored so that you generate the number of pulses

defined in the multipoint write. On buffered sample clock pulse trains the pulse

specifications in the DAQmx Create Counter Output Channel are generated after the

counters starts and before the first sample clock so that you generate the number of

updates defined in the multipoint write.

Finite Implicit Buffered Pulse Train Generation

This function generates a predetermined number of pulses with variable idle and active times.

Each point you write generates a single pulse. The number of pairs of idle and active times (pulse

specifications) you write determines the number of pulses generated. All points are generated

back to back to create a user defined pulse train.

Table 5-6 and Figure 5-32 detail a finite implicit generation of three samples.

S

OURCE

OUT

Co

u

nter Armed