Appendix A

Specifications for Maximum Signal Ratings for AT Series Devices

A-38

ni.com

Electromagnetic Compatibility

CE, C-Tick, and FCC Part 15 (Class A) Compliant

Electrical emissions ................................EN 55011 Class A at 10 m

FCC Part 15A above 1 GHz

Electrical immunity ................................Evaluated to EN 61326:1998,

Table 1

Note

For full EMC compliance, you must operate this device with shielded cabling.

In addition, all covers and filler panels must be installed. Refer to the Declaration of

Conformity (DoC) for this product for any additional regulatory compliance information.

To obtain the DoC for this product, click

Declaration of Conformity

at

ni.com/hardref.nsf/

.

This Web site lists the DoCs by product family. Select the

appropriate product family, followed by the product, and a link to the DoC appears in

Adobe Acrobat format. Click the Acrobat icon to download or read the DoC.

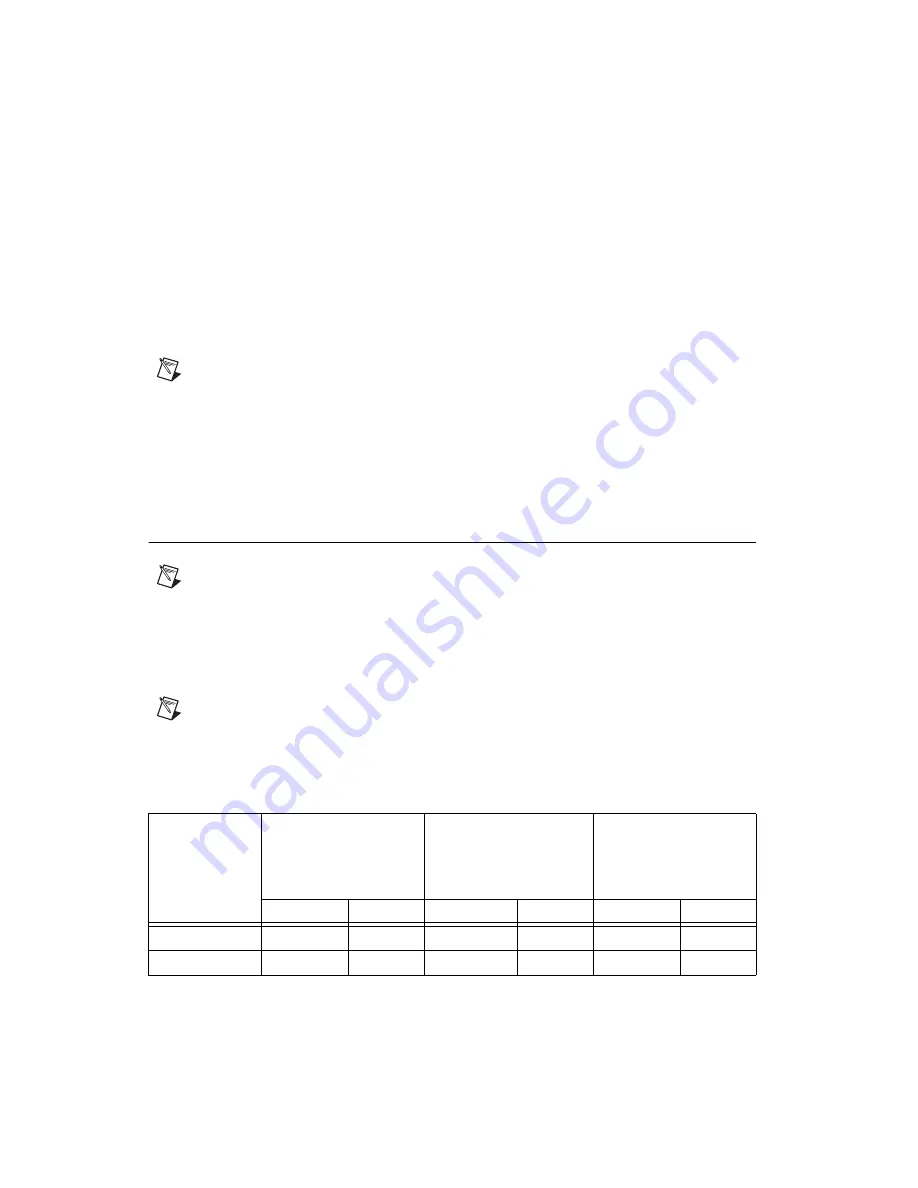

Maximum Signal Ratings for AT Series Devices

Note

NI is

not

liable for any damage resulting from signal connections that exceed these

ratings. Refer to the warranty for specific information on warranty coverage.

Connections that exceed any of the maximum ratings of input signals on the

data acquisition (DAQ) devices listed in the table below can damage the

computer and the device.

Note

These are the absolute maximum ratings of the input signals, not the working

ratings. Refer to the user manual for the recommended operating conditions of the device.

Use the following specifications as definitive values. Signal ratings change

depending on whether the DAQ device is powered on or off.

Signal Name

AT-MIO-16E-1

AT-MIO-16E-2

AT-MIO-64E-3

AT-MIO-16XE-10

AT-AI-16XE-10

AT-MIO-16E-10

AT-MIO-16DE-10

AT-MIO-16XE-50

On

Off

On

Off

On

Off

ACH<

x

>

±25 V

±15 V

±35 V

±25 V

±25 V

±15 V

AISENSE

±25 V

±15 V

±35 V

±25 V

±25 V

±15 V