MYiR-Tech

|

www.myirtech.com

6

/

27

FZ3 Deep Learning Accelerator Card

Hardware Manual

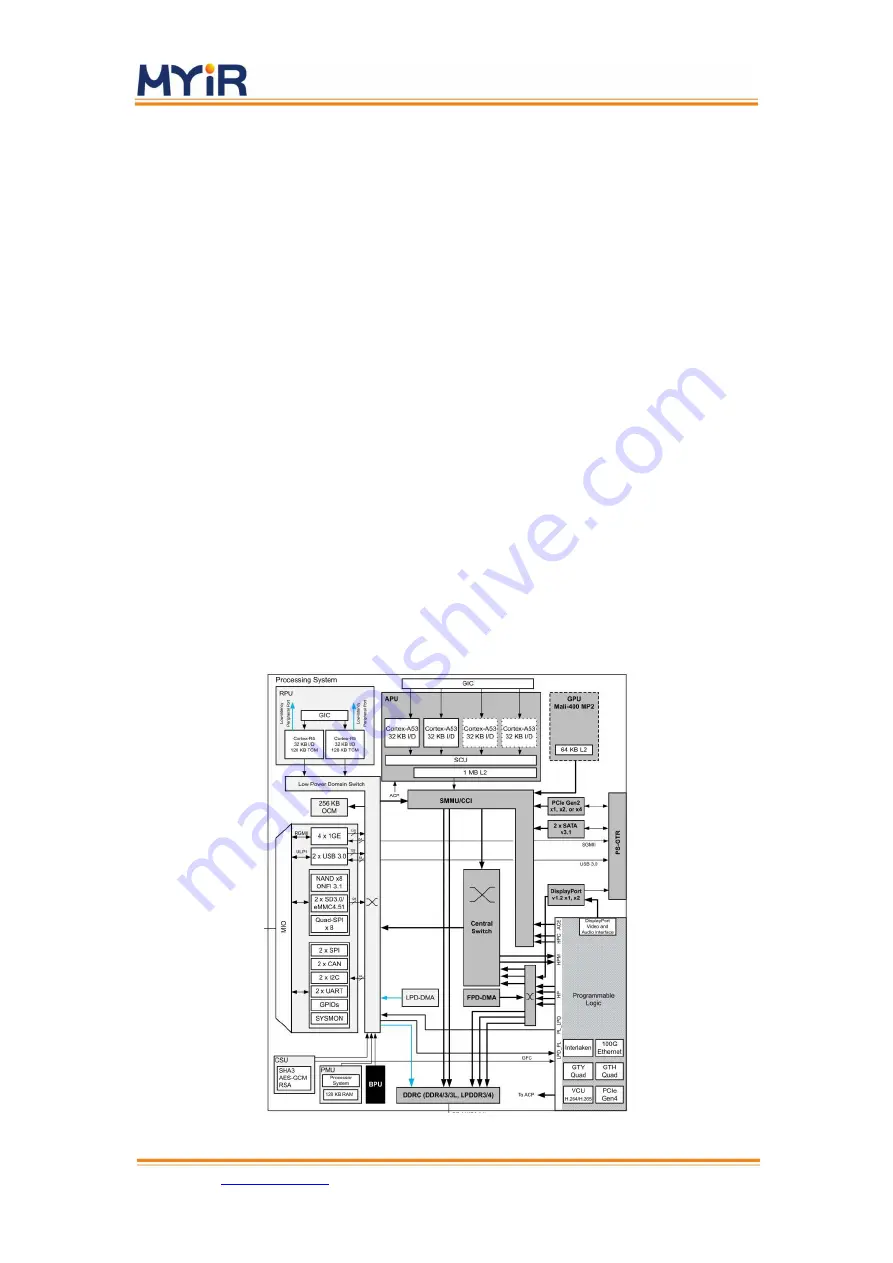

Chapter 2 SOC introduction

2.1 SoC features

The XCZU3EG used in this development platform belongs to the Zynq Ultr

MPSoC series SoC, integrating ARM quad-core Cortex-A53 (PS), dual-core Cortex-R5

(PS), Mali-400 MP2 graphics processing unit and Kintex Ultr FPGA (PL). The

quad-core Cortex-A53 has powerful computing capabilities, the dual-core Cortex-R5 can

be used for real-time processing applications, the Mali-400 MP2 can be used to

accelerate graphics processing, and the FPGA is fully programmable. With the

expandable I / O ports, it can adapt to a variety of application AI development scenarios.

The main chip of the AI development platform uses Xilinx XCZU3EG-SFVC784 devices

with a speed grade of -1 (MYC-CZU3EG SOM is designed to support all speed grades of

XCZU3EG-SFVC784 devices). XCZU3EG-SFVC784 supports 1.5GHz (max -1) APU

speed, 600MHz (max -1) RPU speed, 667MHz (max -1) GPU speed, and DDR4 speed

up to 2400Mbps. The XCZU3EG-SFVC784 device has the following resources:

Figure 2-1