2-30

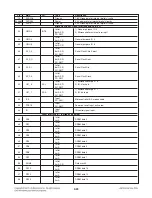

Pin

Main

Alt.

Type

Description

59

RD12

InOut

DRAM data 12

4mA

61

RD11

InOut

DRAM data 11

4mA

62

RD10

InOut

DRAM data 10

4mA

63

RD9

InOut

DRAM data 9

4mA

64

RD8

InOut

DRAM data 8

4mA

65

DQM1

InOut

Data mask 1

4mA, PD

66

RCLK

InOut

Dram clock

4mA, PD

67

RA11

InOut

DRAM address bit 11

4mA, PD

69

RA9

InOut

DRAM address 9

4mA, PD

70

RA8

InOut

DRAM address 8

4mA, PD

71

RA7

InOut

DRAM address 7

4mA, PD

72

RA6

InOut

DRAM address 6

4mA, PD

73

RA5

InOut

DRAM address 5

4mA, PD

74

RA4

InOut

DRAM address 4

4mA, PD

75

RWE#

Output

DRAM Write enable, active low

4mA, PD

76

CAS#

Output

DRAM column address strobe, active low

4mA, PD

77

RAS#

Output

DRAM row address strobe, active low

4mA, PD

78

BA0

InOut

DRAM bank address 0

4mA, PD

80

BA1

InOut

DRAM bank address 1

4mA, PD

81

RA10

InOut

DRAM address 10

4mA, PD

82

RA0

InOut

DRAM address 0

4mA, PD

83

RA1

InOut

DRAM address 1

4mA, PD

85

RA2

InOut

DRAM address 2

4mA, PD

86

RA3

InOut

DRAM address 3

4mA, PD

1) GPIO 7

2) Dram Clock Enable

87

GPIO7

CKE

InOut

3) MS_CLK set A

4mA, PD

4) Audio Mute

5) HSYN/VSYN input

6) C0

GPIO (6)

88

GPIO8

1) GPIO8

2) MS_BS set A

InOut

3) SD_CLK set A

4mA, PD

4) ASDATA2

5) ACLK

Summary of Contents for SH33SD-S

Page 25: ...2 16 4 SLED CONTROL RELATED SIGNAL NO DISC CONDITION FIG 4 1 1 2 3 4 1 2 3 4 ...

Page 27: ...2 18 FIG 7 2 DVD 7 DISC TYPE JUDGEMENT WAVEFORMS FIG 7 1 DVD 1 2 3 IC501 IC501 1 2 3 1 2 3 ...

Page 28: ...2 19 FIG 7 4 CD FIG 7 3 CD 1 2 3 IC501 IC501 1 2 3 1 2 3 ...

Page 29: ...2 20 FIG 8 2 CD 8 FOCUS ON WAVEFORMS FIG 8 1 DVD 1 2 3 1 2 3 4 4 1 2 4 3 IC501 ...

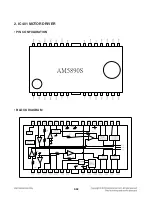

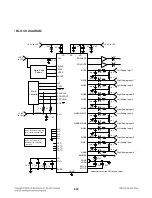

Page 41: ...2 32 2 IC401 MOTOR DRIVER PIN CONFIGURATION BLOCK DIAGRAM ...

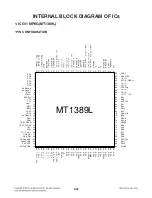

Page 42: ...2 33 1 IC501 MPEG MT1389L PIN DESCRIPTION ...

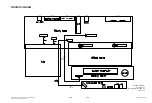

Page 66: ...2 69 2 70 PRINTED CIRCUIT BOARD DIAGRAMS 1 MAIN P C BOARD DIAGRAM TOP VIEW ...

Page 67: ...2 71 2 72 MAIN P C BOARD DIAGRAM BOTTOM VIEW ...

Page 74: ...2 PASSIVE SUBWOOFER SH33SD W 950 A90 951 953 956 954 952 955 WIRE90 3 7 ...

Page 75: ......