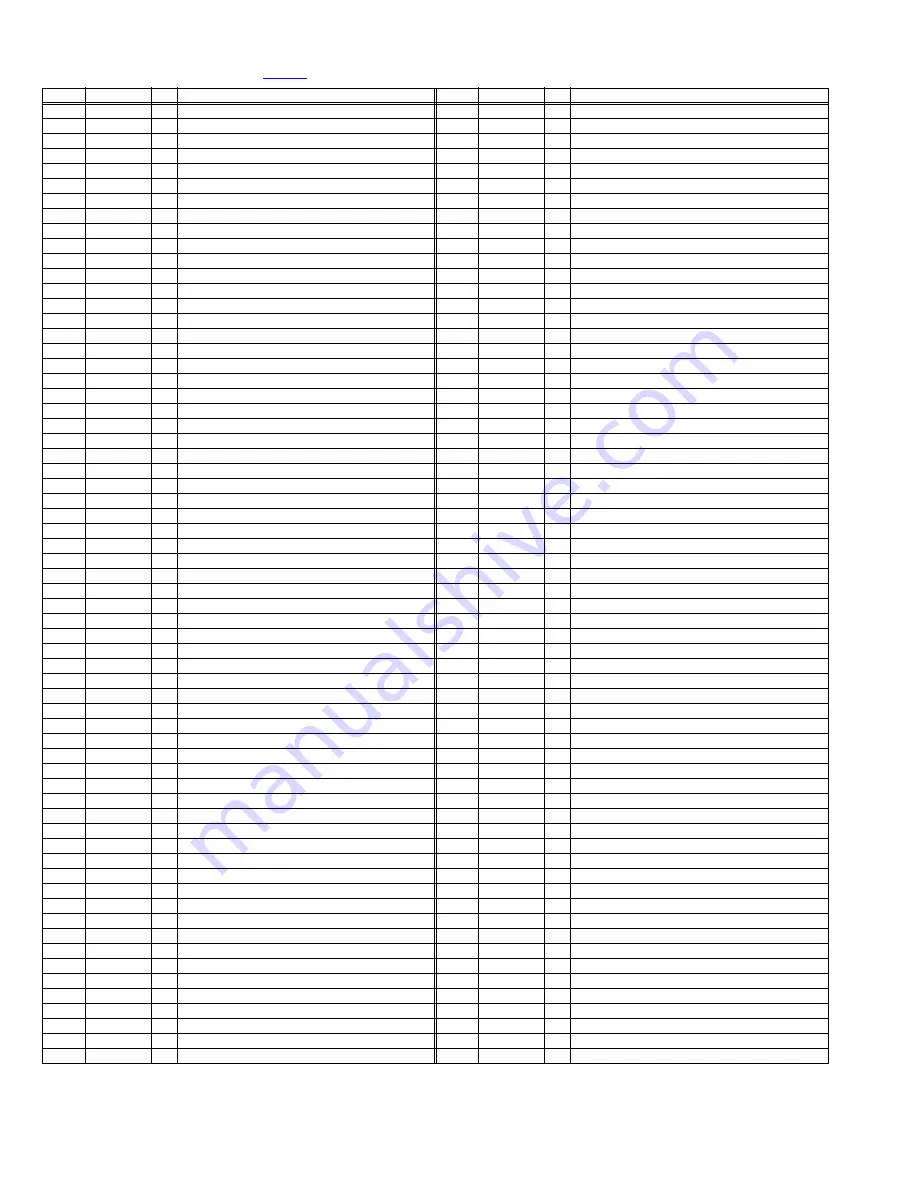

1-8 (No.YA422)

2.4.2 MAIN CPU PIN FUNCTION [

IC7301

: DIGITAL PWB]

Pin

Pin name

I/O

Function

Pin

Pin name

I/O

Function

1

TCK

O

Test purpose

65

D2

I/O Program ROM data for main CPU

2

TMS

I

Test purpose

66

D12

I/O Program ROM data for main CPU

3

TDI

I

Test purpose

67

D10

I/O Program ROM data for main CPU

4

TDO

O

Test purpose

68

VSS33

-

GND

5

P2.8

O

TV, Subtitle/OTHER

69

VDD33

I

3.3V

6

P2.9

O

Blue for OSD

70

D4

I/O Program ROM data for main CPU

7

P2.10

O

Blue for OSD

71

D3

I/O Program ROM data for main CPU

8

P2.11

O

Blue for OSD

72

D11

I/O Program ROM data for main CPU

9

P2.12

O

Blue for OSD

73

RSTIN

I

Reset

10

P2.13

O

Blue for OSD

74

POWER

O

Sleep state release for chassis CPU [Relese : L]

11

P2.14

I

Not used

75

P3.1

O

DM_RESET(IDTV)

12

P2.15

O

Request for chassis CPU communication

76

REMOCON

I

Remote control

13

VSS33

-

GND

77

P3.3

I

Clock for OSD

14

VDD33

I

3.3V

78

P3.4

O

Red for OSD

15

P4.5

O

Not used

79

P3.5

O

Red for OSD

16

A20

O

Program ROM address for main CPU

80

P3.6

O

Red for OSD

17

A19

O

Program ROM address for main CPU

81

P3.7

O

Red for OSD

18

A18

O

Program ROM address for main CPU

82

MTST

I/O Data transmission for chassis CPU communication

19

A17

O

Program ROM address for main CPU

83

MTSR

I/O Data receive for chassis CPU communication

20

VSS25

-

GND

84

VSS33

-

GND

21

VDD25

I

2.5V

85

VDD33

I

3.3V

22

A16

O

Program ROM address for main CPU

86

VSS25

-

GND

23

A8

O

Program ROM address for main CPU

87

VDD25

I

2.5V

24

A7

O

Program ROM address for main CPU

88

TXD0

I/O Communication for adjustment

25

A9

O

Program ROM address for main CPU

89

RXD0

I/O Communication for adjustment

26

A6

O

Program ROM address for main CPU

90

P3.12

O

Red for OSD

27

A5

O

Program ROM address for main CPU

91

CLK

O

Clock for chassis CPU communication

28

A10

O

Program ROM address for main CPU

92

P3.15

O

Green for OSD

29

A11

O

Program ROM address for main CPU

93

P5.14

O

Green for OSD

30

A12

O

Program ROM address for main CPU

94

P5.15

O

Green for OSD

31

VSS33

-

GND

95

TRIG_IN

O

Green for OSD

32

VDD33

I

3.3V

96

TRIG_OUT

O

Green for OSD

33

A4

O

Program ROM address for main CPU

97

P6.2

O

Green for OSD

34

A3

O

Program ROM address for main CPU

98

P6.3

I/O I

2

C bus clock (for main memory)

35

A2

O

Program ROM address for main CPU

99

P6.4

I/O I

2

C bus Data (for main memory)

36

A1

O

Program ROM address for main CPU

100

P6.5

O

Teletext signal select [Analog RGB : H / Digital RGB : L]

37

A0

O

Program ROM address for main CPU

101

IRQ

O

IRQ(IDTV)

38

A13

O

Program ROM address for main CPU

102

VSYNC

I/O Vertical sync

39

ARAS/A14

O

Program ROM address for main CPU

103

HSYNC

I/O Horizontal sync

40

CAS/A15

O

Program ROM address for main CPU

104

COR/RSTOUT

O

Not used

41

VSS33

-

GND

105

BLANK

O

Ys for OSD / Teletext

42

VDD33

I

3.3V

106

VDD33

I

3.3V

43

MEMCLK

O

Clock for memory

107

VSS33

-

GND

44

CSSDRAM

O

Chip select for memory

108

XTAL1

I

6MHz for system clock

45

CLKEN

O

Clock enable for memory

109

XTAL2

O

6MHz for system clock

46

CSROM

O

Chip select for memory

110

VSSA

-

GND

47

RD

O

Read for memory

111

VDDA

I

2.5V

48

UDQM

O

Control buffer of memory

112

R

O

R for OSD / Teletext

49

LDQM

O

Control buffer of memory

113

G

O

G for OSD / Teletext

50

WR

O

Write for memory

114

B

O

B for OSD / Teletext

51

D15

I/O Program ROM data for main CPU

115

VSSA

-

GND

52

VSS33

-

GND

116

VDDA

I

2.5V

53

VDD33

I

3.3V

117

CVBS2

I

Video for Teletext

54

D7

I/O Program ROM data for main CPU

118

VSSA

-

GND

55

D0

I/O Program ROM data for main CPU

119

VDDA

I

2.5V

56

D14

I/O Program ROM data for main CPU

120

CVBS1B

I

Video for Teletext

57

D8

I/O Program ROM data for main CPU

121

CVBS1A

I

Video for Teletext

58

D6

I/O Program ROM data for main CPU

122

VSSA

-

GND

59

D1

I/O Program ROM data for main CPU

123

VDDA

I

2.5V

60

VSS33

-

GND

124

KEY1

I

Key scan data 1 [ON : H]

61

VDD33

I

3.3V

125

KEY2

I

Key scan data 2 [ON : H]

62

D13

I/O Program ROM data for main CPU

126

MECA_SW

I

Main power ON / OFF control [ON : L]

63

D9

I/O Program ROM data for main CPU

127

(KEYP2)P5.3

I

Not used

64

D5

I/O Program ROM data for main CPU

128

TMODE

I

Test purpose