(No.49831)1-35

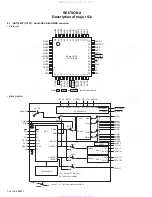

• Pin function

Pin No.

Symbol

I/O

Function

1

AINL3

I

ADC single-ended analog Lch input pin No.3

2

AINR2

I

ADC single-ended analog Rch input pin No.2

3

AINL2

I

ADC single-ended analog Lch input pin No.2

4

AINR1

I

ADC single-ended analog Rch input pin No.1

5

AINL1

I

ADC single-ended analog Lch input pin No.1

6

VREFH

I

Analog Reference voltage input pin.

Normally, connect to AVDD (pin 7), and connect 0.1mF and 10mF capacitors between this pin and

AVSS.

7

AVDD

-

Power supply pin for analog section 3.3V (typ)

8

AVSS

-

Analog ground 0V

9

DVSS

-

Ground pin for digital section 0V

10

DVDD

-

Power supply pin for digital section 3.3V (typ)

11

XTI

I

Master clock input pin

Connect a crystal oscillator between this pin and the XTO pin or input the external CMOS clock signal

XTI pin.

12

XTO

O

Crystal oscillator output pin

When a crystal oscillator is used, it should be connected between XTI and XTO.

When the external clock is used, keep this pin open

13

CLKO

O

Clock output pin Outputs the XTI clock. Allows the output to be set to "L" by control register setting.

14

JX

I

External condition jump pin (Pull down)

15

SMODE

I

Slave/master mode selector pin

Set LRCLK and BITCLK to input or output mode.

SMODE-"L": Slave mode (These are set to input mode.)

SMODE-"H": Master mode (These are set to output mode.)

16

LRCLK

I/O

LR channel select Clock pin

SMODE-"L": Slave mode : Inputs the fs clock.

SMODE-"H": Master mode : Outputs the fs clock.

17

BITCLK

I/O

Serial bit clock pin

SMODE-"L": Slave mode : Inputs 64 fs or 48 fs clocks.

SMODE-"H": Master mode : Outputs 64 fs clocks.

18

SDIN

I

DSP Serial data input pin (Pull down)

Compatible with MSB/LSB justified 24 20 and 16 bits.

19

SDINA

I

DSP Serial data input pin (Pull down)

Leave opens or connect to DVSS at using the internal ADC.

Compatible with MSB justified 24 bits.

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299