1-59

CA-MXS6MDR

SP-MXS6MD

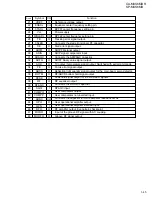

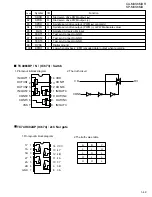

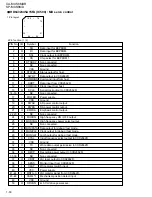

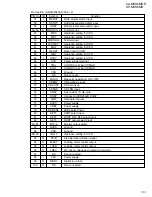

1.Pin layout

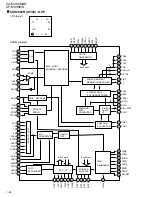

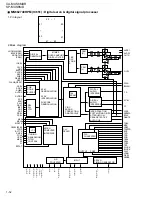

3.Block diagram

2.Pin function

HY51V17400CT-60 (IC390) : DRAM

Vcc

DQ0

DQ1

WE

RAS

A11

A10

A0

A1

A2

A3

Vcc

Vss

DQ3

DQ2

CAS

OE

A9

A8

A7

A6

A5

A4

Vss

Pin Name

Parameter

/RAS

/CAS

/WE

/OE

A0~A11

A0~A10

DQ0~DQ3

Vcc

Vss

NC

Row Address Strobe

Column Address Strobe

Write Enable

Output Enable

Address Input (4K Refresh Product)

Address Input (2K Refresh Product)

Data In/Out

Power (3.3V)

Ground

No Connection

Vcc

Vss

Substrate Bias

Generator

X16 Parallel

Test

RAS Clock

Generator

Row Presecoder

(11/12)*

(11/12)*

RAS

Refresh Counter

Refresh Counter

Address Buff

e

r

Cloumn Predecoder

(11/12)*

CAS Clock

Generator

Data Input Buffer

DQ0~3

DQ0~3

4

4

4

4

Data Output Buffer

(11/10)*

Row

Decoder

Memory Array

4,194,304 x 4

Sense Amp

I/O Gate

Column Decoder

OE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

*(A11)

WE

CAS

DQ0 DQ1 DQ2 DQ3