Intel® Server Board S2600CO Family TPS

Functional Architecture Overview

Revision 1.4

41

Intel order number G42278-004

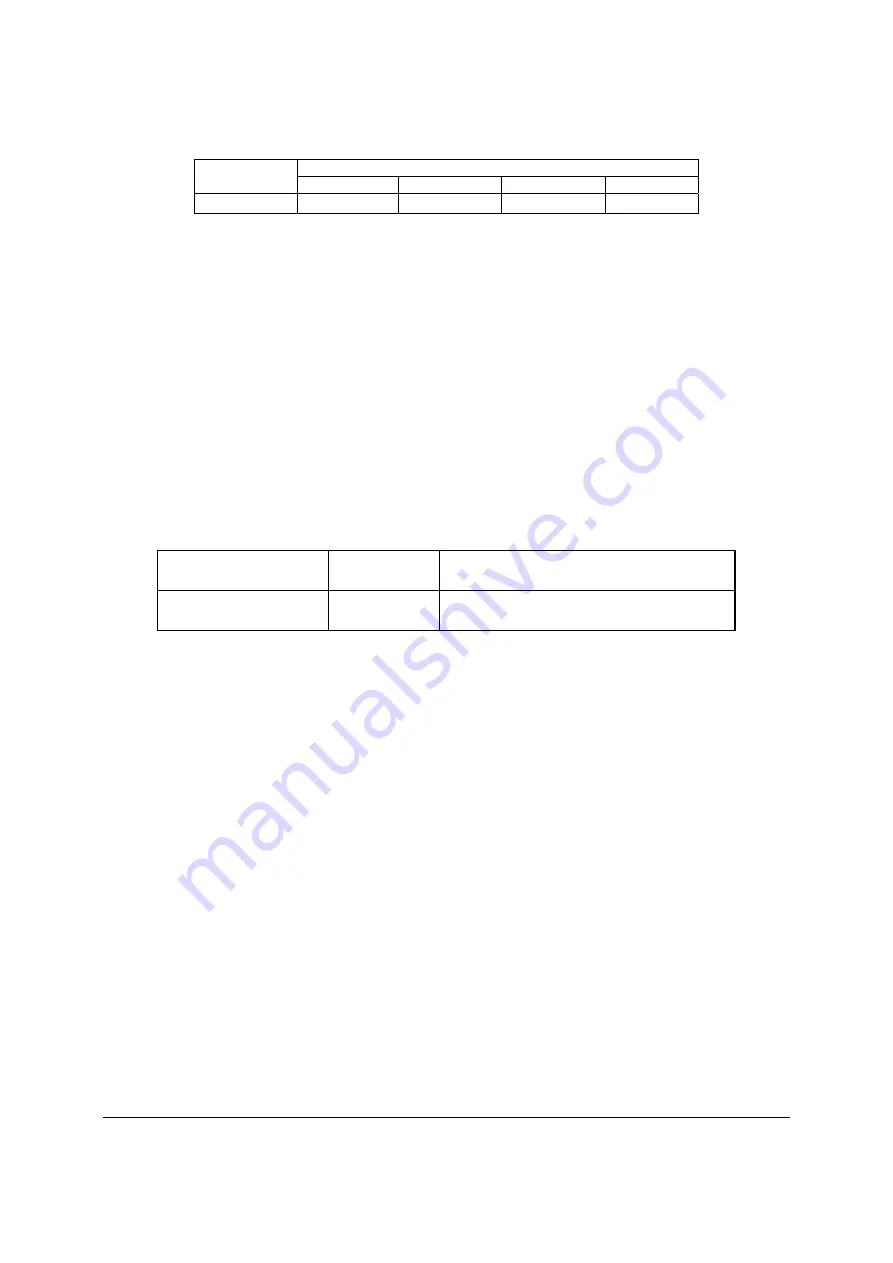

2D Mode

2D Video Mode Support

8 bpp

16 bpp

24 bpp

32 bpp

1600x1200** Supported Supported

** Video resolutions at 1600x1200 and higher are only supported through the

external video connector located on the rear I/O section of the server board.

Utilizing the optional front panel video connector may result in lower video

resolutions.

The server board provides one video interfaces. The video interface is accessed using a

standard 15-pin VGA connector found on the back edge of the server board.

The BIOS supports dual-video mode when an add-in video card is installed.

In the single mode (dual monitor video = disabled), the on-board video controller is disabled

when an add-in video card is detected.

In the dual mode (on-board video = enabled, dual monitor video = enabled), the on-board video

controller is enabled and is the primary video device. The add-in video card is allocated

resources and is considered the secondary video device. The BIOS Setup utility provides

options to configure the feature as follows:

Table 12. Video mode

On-board Video

Enabled

Disabled

Dual Monitor Video

Enabled

Disabled

Shaded if on-board video is set to "Disabled"

3.4.3

Baseboard Management Controller

The server board utilizes the following features of the embedded baseboard management

controller.

IPMI 2.0 Compliant

400MHz 32-bit ARM9 processor with memory management unit (MMU)

Two independent 10/100/1000 Ethernet Controllers with Reduced Media Independent

Interface (RMII)/ Reduced Gigabit Media Independent Interface (RGMII) support

DDR2/3 16-bit interface with up to 800 MHz operation

16 10-bit ADCs

Sixteen fan tachometers

Eight Pulse Width Modulators (PWM)

Chassis intrusion logic

JTAG Master

Eight I

2

C interfaces with master-slave and SMBus* timeout support. All interfaces are

SMBus* 2.0 compliant.

Parallel general-purpose I/O Ports (16 direct, 32 shared)

Serial general-purpose I/O Ports (80 in and 80 out)

Three UARTs

Platform Environmental Control Interface (PECI)

Summary of Contents for S2600CO series

Page 12: ......