Intel® Server Board S2600CO Family TPS

Appendix C: Integrated BMC Sensor Tables

Revision 1.4

Intel order number G42278-004

123

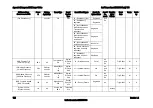

Full Sensor Name

(Sensor name in SDR)

Sensor

#

Platform

Applicability

Sensor Type

Event/

Reading

Type

Event Offset Triggers

Contrib. To

System Status

Assert/

De-

assert

Readable

Value/

Offsets

Event

Data

Rearm

Stand-

by

IPMI Watchdog

(IPMI Watchdog)

03h All

Watchdog 2

23h

Sensor

Specific

6Fh

00 - Timer expired,

status only

OK As

–

Trig Offset

A X

01 - Hard reset

02 - Power down

03 - Power cycle

08 - Timer interrupt

Physical Security

(Physical Scrty)

04h

Chassis

Intrusion is

chassis-

specific

Physical

Security

05h

Sensor

Specific

6Fh

00 - Chassis intrusion

OK

As

and

De

– Trig

Offset

A X

04 - LAN leash lost

FP Interrupt

(FP NMI Diag Int)

05h

Chassis -

specific

Critical

Interrupt

13h

Sensor

Specific

6Fh

00 - Front panel

NMI/diagnostic

interrupt

OK As

–

Trig

Offset

A

–

SMI Timeout

(SMI Timeout)

06h All

SMI Timeout

F3h

Digital

Discrete

03h

01 – State asserted

Fatal

As

and

De

– Trig

Offset

A –

System Event Log

(System Event Log)

07h

All

Event

Logging

Disabled

10h

Sensor

Specific

6Fh

02 - Log area

reset/cleared

OK As

–

Trig

Offset

A

X

System Event

(System Event)

08h All

System

Event

12h

Sensor

Specific

6Fh

02 - Undetermined

system H/W failure

04 – PEF action

Fatal

OK

As

and

De

As

- Trig

Offset

A X

Button Sensor

(Button)

09h All

Button/Switch

14h

Sensor

Specific

6Fh

00 – Power Button

02 – Reset Button

OK AS

_

Trig

Offset

A

X

BMC Watchdog

0Ah

All

Mgmt System

Health

28h

Digital

Discrete

03h

01 – State Asserted

Degraded

As

–

Trig Offset

A

-

Voltage Regulator Watchdog

(

VR Watchdog

)

0Bh All

Voltage

02h

Digital

Discrete

03h

01 – State Asserted

Fatal

As

and

De

– Trig

Offset

M X

Fan Redundancy

Note1

0Ch

Chassis-

Fan

Generic

00 - Fully redundant

OK

As

– Trig

Offset

A –

Summary of Contents for S2600CO series

Page 12: ......