Model No: M150 Plus

Customer: INTEK Rev No: A

13

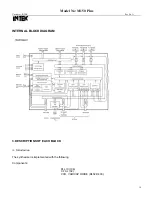

PLL CIRCUIT BLOCK DIAGRAM

1. INTRODUCTION

The frequencies for transmitter and receiver first local frequencies are all derived from a single 4.0 MHz crystal

by means of a phase locked loop. The first local oscillator frequencies are 26.965 MHz (CH 1) to

27.405MHz (CH 40) for EU and 27.60125 MHz (CH 1) to 27.99125 MHz (CH 40) for UK . The second local

frequency is fixed at 10.240 MHz to generate second IF 455 KHz.

The VCO operating frequency for the receiver is 37.660 MHz (CH 1) to 37.560 MHz (CH 40) as the first local

oscillator, injected through the buffer AMP Q411 into the first fed balanced mixer Q2 and Q3.

2. BASIC SYNTHESIZER SCHEME

The crystal frequency (4.000 MHz) is divided by 800 times to make 5 KHz which is fed to one side of the phase

detector. The VCO output is divided by a programmable divider, and fed to other side of the phase detector of

IC4. The feedback loop is closed by passing the phase detector output through an active low pass filter and using

the output to control the VCO frequency through varicap diode D402,D403

Under locked conditions, both of phase detector input signal must be indential at 5 KHz. The VCO frequency is

then given by:

FVCO / N = 0.005 MHz or FVCO = 0.005 x N MHz

Since “N” is an integer, the VCO frequency can be stepped up with 5 KHz increments. By suitable choice of “N”

the desired output frequency can be obtained.

Channel 1

Channel 40

N

FVCO

N

FVCO

FUNCTION

Transmit

5393

26.965

5481

27.405

Receive

7532

37.660

7620

38.100

EU

Transmit

5520.25

27.60125

5598.25

27.99125

Receive

7659.2

38.296

7737.25

38.68625

UK

Since all frequencies are obtained from the crystal controlled PLL oscillator, all outputs are coherent with the

crystal oscillator frequency and maintaining the same percentage accuracy.