2A

3A

4A

5A

6A

7A

8A

1A

2B

3B

4B

5B

6B

7B

8B

1B

2C

3C

4C

5C

6C

7C

8C

1C

2D

3D

4D

5D

6D

7D

8D

1D

2E

3E

4E

5E

6E

7E

8E

1E

2F

3F

4F

5F

6F

7F

8F

1F

DATA2[7]

ROM_PADR[1]

ROM_PADR[2]

ROM_PADR[3]

ROM_PADR[4]

ROM_PADR[5]

ROM_PADR[6]

ROM_PADR[7]

ROM_PADR[8]

ROM_PADR[17]

ROM_PADR[16]

ROM_PADR[15]

ROM_PADR[14]

ROM_PADR[9]

ROM_PADR[10]

ROM_PADR[11]

ROM_PADR[12]

ROM_PADR[13]

OSDBKEY

OSDGKEY

OSDRKEY

SSGSYNC2

ADCK1

SP2A

AD1[9]

AD1[7]

AD1[4]

AD1[1]

AD1[8]

AD1[3]

AD1[5]

AD1[0]

AD1[2]

AD1[11]

AD1[10]

AD1[6]

XV2

XV1

PBLK

CS_CDS1

CS_CDS2_IrisOpen

CS_LENS

VSUB_CONT

OSDFKEY

TD_CS

TD_OE_FLASH

ADJ_Hgin

ADJ_Rgin

OBP

IRIS_PWM

LENSCK

SHUT_CTRL

HALF_FV

XSUB

XSG1

XSG2

XV3

XV4

ROM_PDAT[0]

ROM_PDAT[1]

ROM_PDAT[2]

ROM_PDAT[3]

ROM_PDAT[4]

ROM_PDAT[5]

ROM_PDAT[6]

ROM_PDAT[7]

ROM_DAT15/ADR0

ROM_PDAT[13]

ROM_PDAT[12]

ROM_PDAT[11]

ROM_PDAT[10]

ROM_PDAT[9]

ND_PWM

CS_DAC_HALL_G

ROM_PDAT[14]

H8_RESET

SCI_REQ

DATA2[6]

DATA2[5]

DATA2[4]

DATA2[3]

DATA2[2]

DATA2[1]

ROM_PDAT[8]

CLK1

CLK0

ROM_DAT15/ADR0

OSDGKEY

OSDRKEY

TD_CS

SSGSYNC2

TD_OE_FLASH

CCDSYNC1

OSDFKEY

DATA_MASK

OSDBKEY

AD2[2]

AD2[0]

AD2[1]

AD2[5]

AD2[3]

AD2[6]

AD2[4]

AD2[7]

AD2[9]

AD2[8]

AD2[10]

ADJ_Hgin

ADJ_Rgin

RG

H2

H1

SP1A

OBP

PBLK

ADCK1

CS_CDS1

CS_CDS2_IrisOpen

VSUB_CONT

XV3

XSG2

XV4

XSUB

XV2

XSG1

XV1

AD2[11]

CS_CDS2_IrisOpen

SDO_1

SCK_1

CLK0

CLK0

DATA0[7]

DATA0[7]

THERMO

H_GYR

V_GYR

C1.5V

C1.5V

C1.5V

C1.5V

C1.5V

H_GYR

V_GYR

THERMO

DATA0[6]

DATA0[6]

DATA0[5]

DATA0[5]

DATA0[4]

DATA0[4]

DATA0[3]

DATA0[3]

DATA0[2]

DATA0[2]

DATA0[0]

DATA0[0]

DATA0_TD[0]

DATA0_TD[1]

DATA0_TD[2]

DATA0_TD[3]

DATA0_TD[4]

DATA0_TD[5]

DATA0_TD[6]

DATA0_TD[7]

CLK0_TD

CCDSYNC1

H2

H1

RG

SP1A

CLK1

CLK1

DATA0[1]

DATA0[1]

CLK0

CLK1

SDO

I.O_VCC

I.O_VCC

A_VCC

A_VCC

ZM_NME

DATA_MASK

CLK0_TD

DATA1[0]

DATA1[0]

DATA1[1]

DATA1[1]

DATA1[2]

DATA1[2]

DATA1[3]

DATA1[3]

DATA1[4]

DATA1[4]

DATA1[5]

DATA1[5]

DATA1[6]

DATA1[6]

DATA1[7]

DATA1[7]

SP2A

DATA2[0]

C2317

C2316

C2318

C2312

0.01/16

C2313

0.01/16

C2314

0.01/16

C2320

0.01/16

4

2

3

2

C

6

1

/

1

0

.

0

C2319

22/6.3

5

2

3

2

C

6

1

/

1

0

.

0

6

2

3

2

C

6

1

/

1

0

.

0

C2308

2.2/6.3

C2307

0.1/10

C2322

0.01/16

0.01/16

0.01/16

0.01/16

C2327

0.01/16

C2328

0.01/16

*

C2329

C2306

1/10

C2304

0.1/10

C2303

2.2/6.3

C2346

0.01/16

C2345

0.01/16

C2343

0.01/16

C2340

0.01/16

C2338

0.01/16

C2335

0.01/16

C2333

0.01/16

C2344

0.01/16

C2341

0.01/16

C2339

0.01/16

C2336

0.01/16

C2334

0.01/16

C2332

0.01/16

C2311

22/6.3

22/6.3

C2315

C2347

0.01/16

C2348

0.01/16

C2349

0.01/16

C2350

0.01/16

C2342

22/6.3

C2300

0.1/10

C2301 0.1/10

C2321

0.1/10

C2323

0.1/10

C2330

68p/50

C2331

33p/50

C2351

10p/50

.

*

C2309

C2310

C2305

100/6

V

D2301

RB521S-30

RB521S-30

*

D2300

T/W

AD1[0-11]

H8COMDO

EXT_CIN

DATA_MASK

CS_EE_TC

EXT_YIN

SCK_3M

CLK1

DATA1[0-7]

CLK0

OSDRKEY

OSDGKEY

OSDBKEY

OSDFKEY

H8COMCK

SDO

SYS_RESET

DATA0[0-7]

CLK0_TD

DATA0_TD[0-7]

C5V

X1I

8FSC

GND

C3V_SYS2

F_DET

ND_DET

C3V_SYS

C1.8V

PLL_STB

3M_RESET

RD

SCI_3M

SHOE_DET

SHOE_REG

H8_RESET

ROM_DAT15/ADR0

ROM_PDAT[0-14]

ROM_PADR[1-17]

DATA2[0-7]

DATA1[0-7]

DATA0[0-7]

B_OUT

SSG_HDO

SSG_FVO

HALL_ADJ0

HALL_ADJ1

VSUB_CONT

C1.5V

C_OUT

Y_OUT

STB_ON

LENSCK

SHOE_SDATA

G_OUT

ADJ_Rgin

ADJ_Hgin

SP2A

CS_CDS2_I

risOpen

DATA_MASK

CCDSYNC1

ND_PWM

CS_DAC_HALL_G

SSGSYNC2

CLK0

SP1A

SDO_1

R_OUT

SHUT_CTR

L

CS_LENS

SCK_1

HALF_FV

SD

SCI_3M

IRIS_PWM

SCI_REQ

SDO

FOCUS_SEN

ZOOM_SEN

EXT_CIN

LED_CONT

GYR_RST

V_GYR

H_GYR

THERMO

SCK_3M

SDO

SLD_3M

ZM_NME

CLK1

CS_CDS2_IrisOpen

CS_CDS1

SCK_1

SDO_1

XV1

XSG1

XV2

XSUB

XV4

XSG2

XV3

H1

H2

RG

CLK2

TD_OE_FLASH

TD_CS

AD2[0-11]

CCDSYNC1

ADCK1

PBLK

SHOE_SCLK

OBP

L2303

3.3

L2305

10

L2300

10

L2301

10

L2302

10

L2304

68

1

CTL

2

GND1

3

Np

4

Vout

5

GND2

6

Vin

Q2300

SUT485J

6

5

4

3

2

1

Q2304

RT1N144U-T111-1

Q2301

2SA1989-T111-1

*

R2367

*

R2366

R2368

56

R2330

27

k

0.5%

R2329

6.8

k

0.5%

R2331

6.8

k

0.5%

R2328

22k

R2334

4.7k

R2304

1k

R2336

4.7k

R2337

4.7k

*

R2369

*

R2335

R2338

1k

1k

0

*

R2365

R2344

100k

R2342

100k

R2371

22

R2348

22

*

R2319

*

R2317

R2313

100k

R2353

10k

R2312

10k

R2379

22

*

R2310

*

R2311

R2314

0

R2309

0

R2378

22

*

R2305

R2339

39k

R2377

22

R2375

22

R2308

33k

R2307

22k

R2306

4.7k

*

R2320

R2321

51

0

1

R2323

51

0

1

R2325

51

0

1

R2322

68k

R2324

47k

R2374

22

R2326

6.8k

R2372

22

*

R2352

R2332

51

0

1

R2333

560

*

R2361

*

R2360

*

R2359

*

R2358

R2341

1k

R2345

3.3k

R2347

2.2k

*

R2357

R2349

3.9k

R2351

680

*

R2356

R2340

51

0

1

R2343

150

*

R2355

*

R2354

*

R2362

*

R2364

R2350

2.2k

R2376

22

R2373

22

IC2300

BR9016ARFV-WE2

CS

1

GND 5

VCC 8

R/B 7

WC 6

DI

3

DO

4

SK

2

G1

1

A2 5

Vcc 8

G2 7

Y1 6

Y2

3

GND

4

A1

2

*

R2318

TL2300

TL2301

TL2303

TL2302

L2306

10

C2352

10/6.3

IC2303

TWINKLE-D

B1

I/O_VCC1

A1

TM2

D1

TMS

E4

TRS

E1

MCK_SEL

F4

VBN

D2

VBBEN

C2

TEST_MODE

F1

CORE_VCC1

G4

D1[6]

E2

D1[10]

D4

D1[11]

G1

CORE_GND1

H4

D1[2]

F2

SCAN_MODE

E5

D1[9]

G2

D1[7]

J4

D1[1]

H1

D1[4]

F5

D1[8]

H2

D1[3]

G5

D1[5]

K4

D1[0]

J2

D2[10]/A[10]

H5

D2[11]/A[11]

K1

D2[8]/A[8]

J5

D2[9]/A[9]

K2

D2[7]/A[7]

L4

D2[4]/A[4]

L1

CORE_VCC2

K5

D2[6]/A[6]

L5

D2[3]/A[3]

L2

D2[5]/A[5]

M4 D2[1]/A[1]

M1 CORE_GND2

M5 D2[0]/A[0]

M2 D2[2]/A[2]

N5

Vrin_port20

N4

Hdi_port21

N2

Reset

P5

H8_Reset

P1

SCK_0

R5

SDI_0

P2

SDO_0

P4

SCI_0_MODE

R1

CORE_VCC3

T5

SCI_REQ

R2

SDO_1

W2 SLD

T1

CORE_GND3

R4

SCK_1

T2

SDI_2

AA3 SDO_2

U1

DRV_OSD_CLK

T4

PWM0

U2

PWM1

U4

NMI

V1

Port1_int1

V2

Port2_int2

W1 Port3_int3

Y2

Port4_int4

Y1

I/O_GND2

AA2

I/O_VCC3

AA1

Port5

AA4

Port6

V5

Port7

AA5

Port8

V6

Port9

Y4

Port10

Y3

Port11

AA6

Port12

V7

Port13

Y5

Port14

V4

Port15

AA7

TDI

V8

Port16

Y6

I/O_GND3

U5

A_GND1

Y7

R_OUT

V9

A_VCC1

AA8

G_OUT

U6

A_VCC2

Y8

REXT1

U7

CBU1

AA9

A_GND2

V10

B_OUT

Y9

A_GND3

U8

A_VCC3

AA10

Y_OUT

U9

A_GND4

Y10

REXT2

V11

CBU2

AA11

A_VCC4

U10

C_OUT

U11

A_GND5

Y11

CORE_VCC4

V12

CORE_GND4

AA12

I/O_VCC4

U12

TDO

Y12

Port17

U13

SYNC1_Port18

AA13

SYNC2_Port19

V13

SSG_HD

Y13

SSG_FV

U14

CCDSY

NC1_Port2

2

AA14

SSGSYNC2_Port23

U15

OSDRKey_Port24

Y14

OSDGKey_Port25

V14

OSDBKey_Port26

AA15

OSDFKey_Port27

U16

DQ[15]

Y19

DQ[13]

AA16

DQ[12]

V15

DQ[11]

Y16

DQ[10]

W21

I/O_GND4

AA17

DQ[9]

V16

DQ[8]

Y17

DQ[7]

V17

DQ[6]

AA18

DQ[5]

Y18

DQ[4]

Y20

DQ[2]

AA20

DQ[1]

Y21

I/O_VCC5

AA21

DQ[0]

V21

CSN

U18

OEN

U21

I/O_GND5

T18

WEN

V20

A[17]

W20

A[16]

T21

CORE_GND5

R18

A[15]

U20

A[14]

V18

A[13]

R21

CORE_VCC5

P18

A[12]

T20

A[11]

U17

A[10]

R20

A[9]

N18

A[8]

T17

A[7]

P20

A[6]

R17

A[5]

N21

I/O_GND6

M18

A[4]

N20

A[3]

P17

A[2]

N17

A[1]

M20

A[0]

L18

Data2[7]

L21

CORE_VCC6

M17

Data2[6]

L17

Data2[5]

L20

Data2[4]

K18

Data2[3]

K21

I/O_GND7

K17

Data2[2]

K20

Data2[1]

J17

Data2[0]

J21

I/O_VCC7

J18

Data1[7]

J20

Data1[6]

H17

Data1[5]

H21

CORE_GND7

G17

Data1[4]

H20

Data1[3]

H18

Data1[2]

G21

CORE_VCC7

F17

Data1[1]

G20

Data1[0]

C20

Data0[7]

F21

I/O_GND8

G18

Data0[6]

F20

Data0[5]

A19

Data0[4]

E21

Data0[3]

F18

Data0[2]

E20

Data0[1]

E18

Data0[0]

D21

I/O_VCC8

D20

CLK2

C21

CLK1

B20

CLK0

B21

I/O_GND9

A20

A.C_GND1

A21

A.C_VCC1

A18

DA0

D17

DA1

A17

AN0

D16

AN1

B18

AN2

B19

A.C_GND2

A16

AN3

D15

AN4

B17

AN5

D18

A.C_VCC2

A15

Vinp

D14

CAL_C

B16

BIAS

E17

A.C_VCC3

B15

VRT

D13

VRT_C

A14

VR1

E16

VRB

B14

VRB_C

E15

Vinn

A13

A.C_GND3

D12

I/O_GND10

B13

MBIST_TESET_H

E14

TCK

A12

PBLK

E13

OBP

B12

BUS_SEL

D11

XSG3

A11

CORE_GND8

E12

XV1

E11

XV2

B11

XV3

D10

XV4

A10

CORE_VCC8

E10

XSG2

B10

XSG1

E9

XSUB

A9

MAIN_CLK

D9

I/O_VCC9

B9

X1o

E8

X1i

A8

I/O_GND11

E7

I/O_GND_TG1

B8

ADJ_H1in

D8

ADCK1

E6

I/O_VCC_TG1

B7

SP1A

A6

CORE_VCC_TG

D7

ADJ_Rgin

B6

SP1B

C1

SP2B

A5

I/O_VCC_TG2

D6

RG

B5

H1

A4

I/O_GND_TG2

B4

PLL_GND1

A3

PLL_VCC1

B2

PLL_VCC2

A2

PLL_GND2

J1

I/O_GND1

N1

I/O_VCC2

Y15

DQ[14]

AA19

DQ[3]

P21

I/O_VCC6

M21

CORE_GND6

D5

H2

B3

SP2A

A7

CORE_GND_TG

*

R236

3

GND

1/10

56

56

56

56

56

0

0

100/6

1k

1k

47k

220k

1k

0

0

0

0

0

0

0

0

0

0

100/

6

VCO XXX

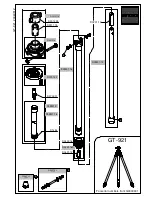

Name of circuit diagram

The following shows the name of circuit to

which signal is connected and the address:

To

PC

Address

(1F)

Note: For parts whose circuit numbers are marked *,

the values and whether they are mounted vary

depending on the model/destination.

See "Parts Search System" to check for the values

and whether they are mounted.

CAMERA DSP [MAN]

A

4

3

2

1

A

B

C

D

E

F

A

B

C

D

E

F

8

7

6

5

4

3

2

1

8

7

6

5

S - 11

S-11 CAMERA DSP [MAN]

P