21

S5U1C33001H

(Ver. 4)

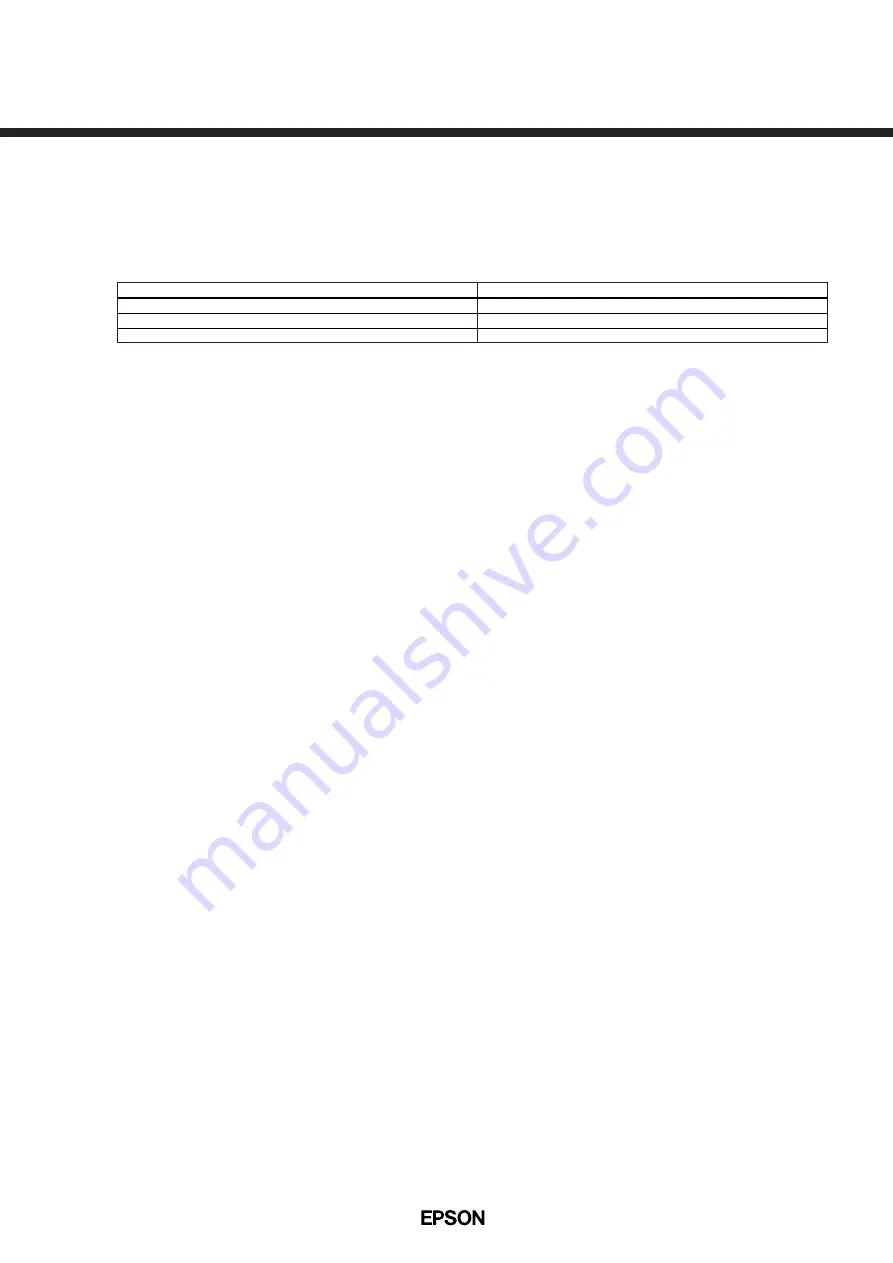

• Counts of the execution counter

The S5U1C33001H's execution counter is normally subject to the errors shown in the table below. These errors must be

taken into account when calculating execution times. Note that execution and break overhead adds the prefetch cycles

for two additional instructions, making the counters usable for only relatively long intervals. For short intervals, use the

clock cycle counts from the trace function.

Table 11 Execution Counter Error

Execution counter

Cycle counter

µ

s-unit time counter

Second-unit time counter

Count error

±

4 bus clock cycles

±

50 ns

±

1

µ

s

• Reserved areas in the internal peripheral circuits (C33 STD/Mini core)

When reserved areas in the internal peripheral circuits are displayed using the S5U1C33001H's data display function,

note that, depending on the type of microcomputer, the last value read by the C33 core that is held in the bus latch circuit

inside the chip may be displayed.

• Operating clock of the S5U1C33001H (C33 STD/Mini core)

When execution of the target program is suspended, the operating clock of S1C33xxx chip on the target system is

forcibly switched to the high-speed clock even if the C33 core may have been operated with the low-speed clock while

the target program was executed. For this reason, if the high-speed clock is turned off by the target program when the

target system is being operated with the low-speed clock, the S5U1C33001H will be unable to operate normally after

execution of the target program is suspended.

• Area 2 of S1C33xxx (C33 STD/Mini/ADV core)

Area 2 of the S1C33xxx (0x0060000 to 0x007FFFF) is reserved as a dedicated area for the programs that operate the

S5U1C33001H. Therefore, no device can be mapped to this area using a parameter file, and data cannot be written to

this area when the target program is suspended or being executed. If the contents of area 2 are rewritten, the

S5U1C33001H will be unable to operate normally. For details on the parameter file, refer to the "Debugger" section in

the "S5U1C33001C Manual (C Compiler Package for S1C33 Family)".

• Concurrent use of the S5U1C330M2S debug monitor

The S5U1C330M2S cannot be used with the S5U1C33001H simultaneously for debugging the target program.

The S5U1C33001H can be used for debugging the S5U1C330M2S. In this case, the S5U1C330M2S must be imple-

mented using "mon33ice.lib" (library supplied with the S5U1C330M2S package). However, only the following parts in

the S5U1C330M2S can be debugged:

- Part for initial connection to the debugger (gdb.exe)

- Confirming the command functions except for execution commands

- Part for communication to the debugger (gdb.exe)

• Reset sequence

The sequence from when the S5U1C33001H is powered on until the execution of the target program is executed is

entirely different from that of the actual S1C33xxx chip.

However, a sequence for the reset requests input from the target system while the target program is being executed is

the same as that for the actual S1C33xxx chip.

Regarding the reset sequence in the actual S1C33xxx chip, refer to the "S1C33xxx Technical Manual".

• Break functions when a reset request is accepted

If a cold reset request from the target system is accepted when the target system is being executed, the hardware PC

break and data break functions are disabled until execution of the target program is suspended.

In the case of a hot reset request, there is no such restriction.

• I/O memory dump by the S5U1C33001H

Note that some S1C33xxx peripheral circuits may change the control register status due to their specifications when the

I/O memory is read using the memory dump function of the S5U1C33001H or when the target program execution is

suspended.

For details on the memory dump function, refer to the "Debugger" section in the "S5U1C33001C Manual (C Compiler

Package for S1C33 Family)".