2

S5U1C33001H

(Ver. 4)

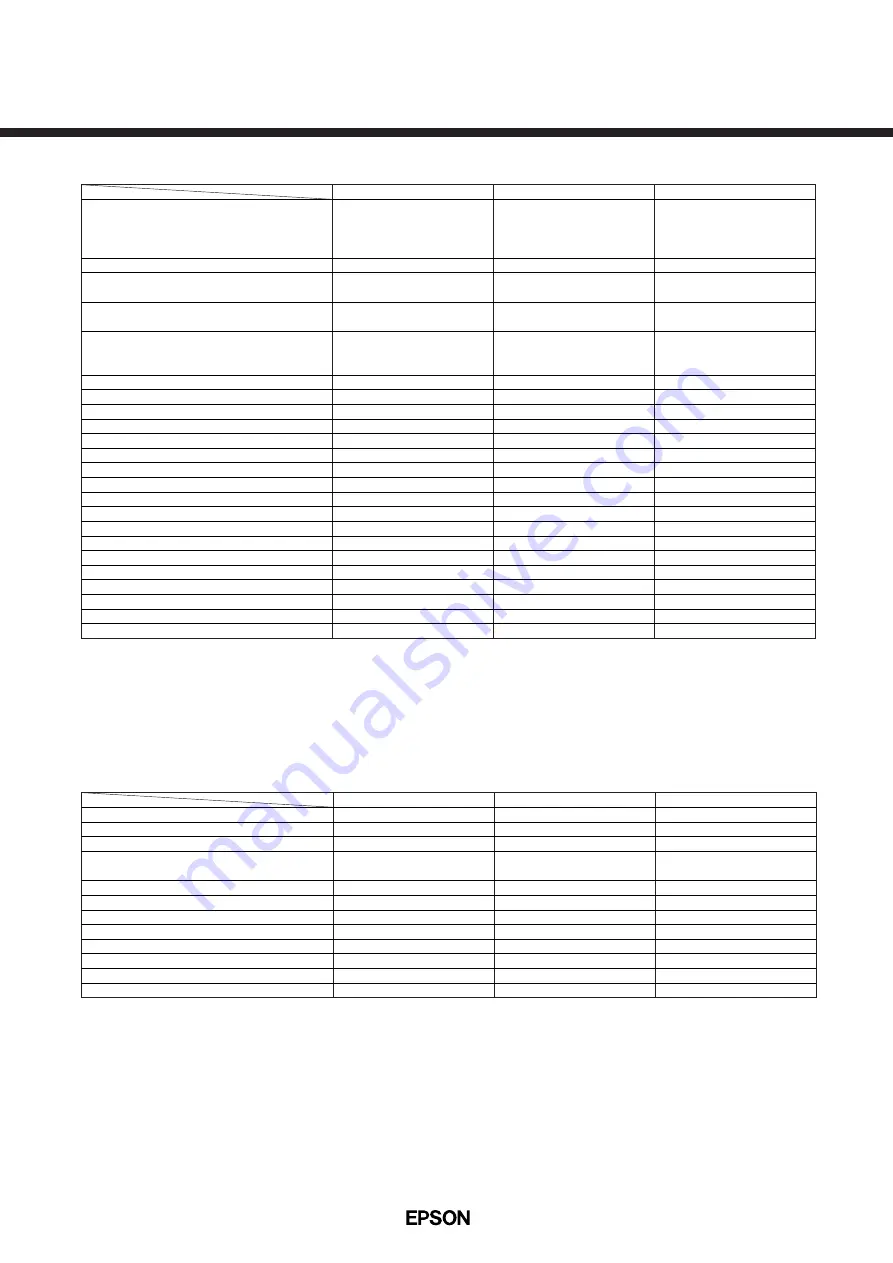

Table 1 ICD Models and Differences

Function

Model

C33 cores supported

Interface with the host PC

Data download speed

∗

1

(maximum rate: DCLK = 40 MHz)

Clock frequency to communicate with the

target

∗

1

Core clock frequency for using the trace

function

∗

1

Maximum trace capacity

Flash programmer function

Firmware update function

Debugger mode

Bus trace function

∗

4

Bus break trigger trace function

∗

4

TRC IN pin input signal trace function

∗

4

User logic signal trace function

∗

4

Target power supply

Target reset signal output

Target system I/O interface voltage

RESET/WRITE switch

DIP switch

Jumper switch for monitoring power supply

LEDs for flash programmer

Target system interface connector

Target system interface method

Target power supply connector

S5U1C33000H

C33 STD core

C33 Mini core

C33 PE core

Serial and parallel I/F

Serial I/F: Approx. 8KB/s

Parallel I/F: Approx. 30KB/s

1 MHz to 40 MHz

1 MHz to 60 MHz (3.3 V)

(4 or 10-pin cable)

128K clock cycles

–

–

ICD2 mode

–

–

–

–

–

–

3.3 V

–

4 bits

–

–

10 pins

4 pins, 10 pins

–

S5U1C33001H (Ver. 3)

C33 STD core

C33 Mini core

C33 PE core

USB 1.1

About 65KB/s

(About 50KB/s at 20 MHz)

1 MHz to 40 MHz

1 MHz to 60 MHz (3.3 V)

(4 or 10-pin cable)

1M clock cycles

Available

–

ICD3 mode

–

–

–

–

–

–

3.3 V

Available

8 bits

Available

Available

10 pins

4 pins, 10 pins

–

S5U1C33001H (Ver. 4)

C33 STD core

C33 Mini core

C33 PE core

C33 ADV core

USB 1.1

About 65KB/s

(About 50KB/s at 20 MHz)

1 MHz to 40 MHz

∗

3

1 MHz to 100 MHz (3.3 V)

∗

2,

∗

3

(4 or 10-pin cable,

or 30-pin coaxial cable)

1M clock cycles

Available

Available

ICD3 mode

Available

Available

Available

Available

3.3 V and 1.8 V

Available

3.3 V or 1.8 V

Available

8 bits

Available

Available

10 pins, 30 pins

4 pins, 10 pins, 30 pins

6 pins

∗

1

Indicates the specifications for 3.3-V I/O. The upper-limit value may be lowered by environment noise, temperature condition, S1C33

model, unevenness in quality, etc.

Note: In the model with the C33 STD or Mini core embedded, the maximum CPU core clock frequency is 60 MHz but the

maximum BCU (bus) clock frequency is 40 MHz. When operating the CPU with a clock higher than 40 MHz, the BCU

clock must be setup to 1/2 CPU core clock (#X2SPD = 0).

∗

2

The maximum frequency may be half or less of the described value when the I/O voltage is 1.8 V.

∗

3

Supports 32 kHz by firmware update.

∗

4

These functions are available only when the core that supports them is used (see the table below).

Table 2 Correspondence between C33 Core and Debug Functions

Function

Core

DCLK while the program is halted

DCLK while the program is being executed

PC trace method

Switching the DCLK-core clock ratio

(DCLK while the program is halted)

Address setup for the debug unit

Area break function

Bus break function

Bus trace function

Bus break trigger trace function

TRC IN pin input signal trace function

User logic signal trace function

Use of MMU in debug mode

C33 STD/Mini

= Bus clock

= Core clock

Level 1

–

–

–

–

–

–

–

–

–

C33 PE

= Core clock

×

set value

∗

5

= Core clock

Level 1

Available

Available

–

–

–

–

–

–

–

C33 ADV

= Core clock

×

set value

∗

5

= Core clock

Level 2

Available

–

Available

Available

Available

Available

Available

Available

∗

6

Available

∗

5

1/1 to 1/8 (1/4 by default) can be selected by the DIP switch. See "DCLK-core clock ratio setting" in the "DIP Switches" section.

∗

6

Available only when the S1C33 model that supports the user logic signal trace function is used.

Level 2 is a PC trace method upwardly compatible with Level 1. It realizes higher analytical accuracy than Level 1.

Functions that are not included in the table above can be used regardless of the core model.