PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

79

Sleep and Watchdog

10.4

Timing Diagrams

10.4.1

Sleep Sequence

The SLEEP bit in the CPU_SCR0 register, is an input into

the sleep logic circuit. This circuit is designed to sequence

the device into and out of the hardware sleep state. The

hardware sequence to put the device to sleep is shown in

1. Firmware sets the SLEEP bit in the CPU_SCR0 register.

The Bus Request (BRQ) signal to the CPU is immedi-

ately asserted: This is a request by the system to halt

CPU operation at an instruction boundary.

2. The CPU issues a Bus Request Acknowledge (BRA) on

the following

of the CPU clock.

3. The sleep logic waits for the following

of

the CPU clock and then asserts a system wide Power

Down (PD) signal. In

, the CPU is halted and

the system wide PD signal is asserted.

The system wide PD signal controls three major circuit

blocks: the Flash memory module, the Internal Main Oscilla-

tor (6/12 MHz oscillator that is also called the IMO), and the

bandgap voltage reference. These circuits transition into a

zero power state.

The only operational circuits on the device in standby sleep

mode are the ILO, the bandgap refresh circuit, and the sup-

ply voltage monitor circuit. In standby sleep mode the supply

voltage monitor circuit is active only during the buzz interval.

To properly detect and recover from a VDD brown out condi-

tion, the configurable buzz rate must be frequent enough to

capture the falling edge of VDD. If the falling edge of VDD is

too sharp to be captured by the buzz rate, any of the follow-

ing actions must be taken to ensure that the device properly

responds to a brown out condition.

■

Bring the device out of sleep before powering down.

This can be accomplished in firmware, or by asserting

XRES before powering down.

■

Assure that VDD falls below 100mV before powering

back up.

■

Set the No Buzz bit in the OSC_CR0 register to keep the

voltage monitoring circuit powered during sleep.

■

Increase the buzz rate to assure that the falling edge of

VDD will be captured. The rate is configured through the

PSSDC bits in the SLP_CFG register.

In deep sleep mode the ILO, bandgap refresh circuit and

supply voltage monitor circuit are all powered down. How-

ever, additional low-power voltage monitoring circuitry gets

enabled when entering deep sleep. This additional low-

power voltage monitoring circuitry allows VDD brown out

conditions to be detected for edge rates slower than 1V/ms.

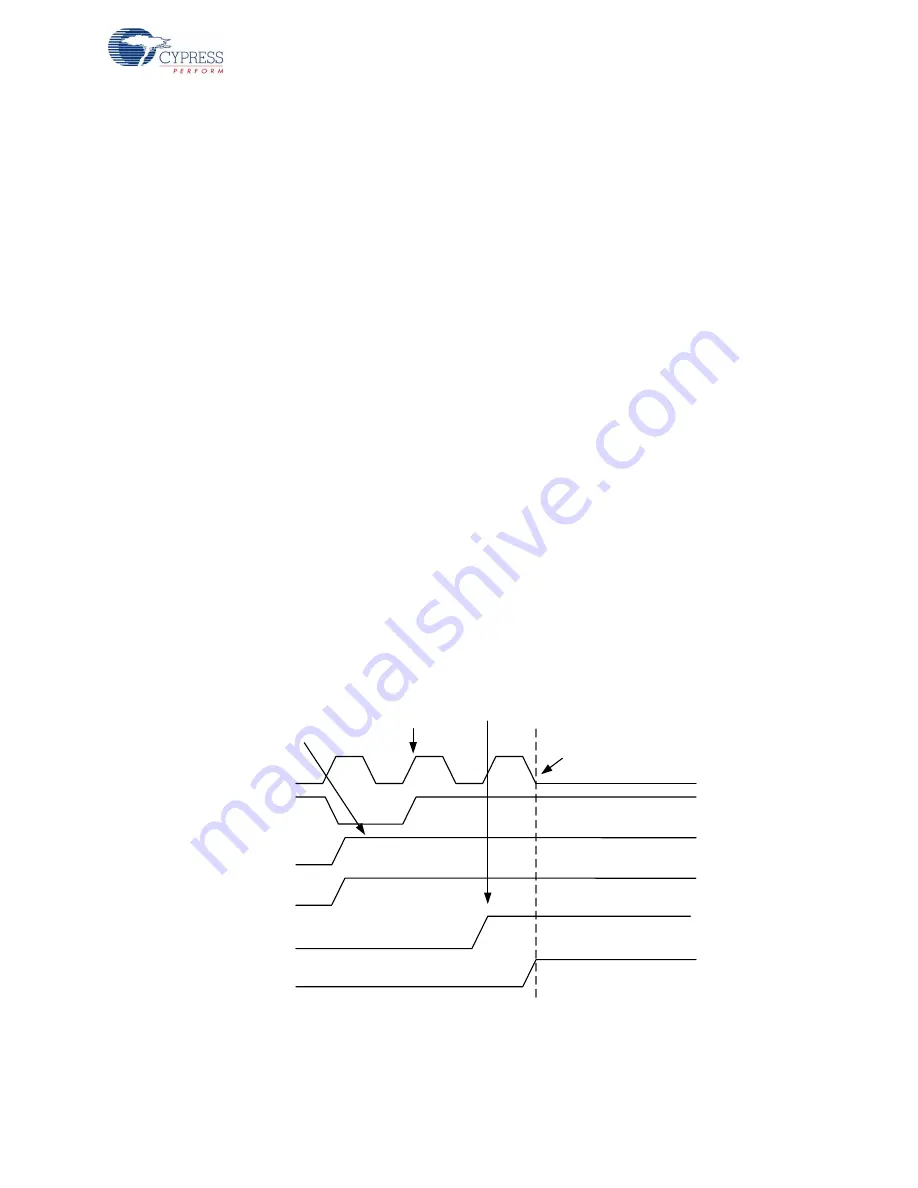

Figure 10-3. Sleep Sequence

IOW

SLEEP

BRQ

BRA

PD

On the falling edge of

CPUCLK, PD is asserted.

The system clock is halted;

the Flash and bandgap are

powered down.

CPUCLK

Firmware write to

the SLEEP bit

causes an

immediate BRQ.

CPU captures

BRQ on next

CPUCLK edge.

CPU responds

with a BRA.

Summary of Contents for PSoC CY8CTMG20 Series

Page 4: ...4 Contents Overview Feedback...

Page 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Page 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Page 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Page 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Page 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Page 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Page 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...