II - 9

1.3.7

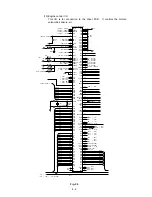

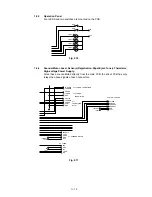

EEPROM

The EEPROM is X24CO1A type of a two-wire method with a 128 x 8 bit configuration.

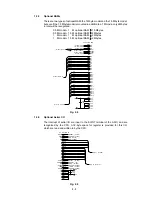

1.3.8

Reset circuit

The reset IC is PST593DMT.

The reset voltage is 4.2 V (typ.) and the LOW period of reset is 200 ms (typ.).

1.3.9

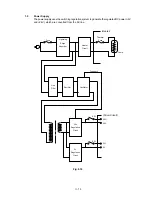

CDCC I/O

C31

104

+5V

0V

SDA (

-05D)

5

8

4

7

R20

4.7K

SDA

VCC

VSS

TEST

SDA

6

1

2

3

(

-05E) SCL

A0

A1

A2

#6

XL24C01AF

+5V

Fig. 2.10

+5V

#7

PST593DMT

3

4

VCC

CND MR

OUT

1

2 NC

R22

1K

C30

102

0V

RESET (

-01E)

Fig. 2.11

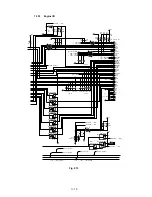

101 X5

C52

C51

C53

C48

C37

0V

ACK (01-05B)

BUSY (01-05B)

PE (01-05B)

SLCT (01-05B)

FLT (01-05B)

PRMINT (01-04A)

SELIN (01-04A)

HBUSY (01-04A)

STB (01-04A)

DC18

DC17

DC16

DC15

DC14

DC13

DC12

DC11

DCI(8..1) (01-03C)

C45

C44

C43

C38

C36

C41

0V

C47

C42

C54

C49

101 X12

C50

C39

RAS 100

1

2

6

5

1

7

6

5

8

7

3

4

8

2

3

4

RA3

100

4

7

3

8

5

2

6

1

100

RA1

5 7 3 8

7 8 6 5

7 8 6 5

4

3

1

2

4

3

1

2

1

6

2

4

RA2

1K

1K

1K

RA4

RA6

+5V

P4 CDCC

10

11

12

13

32

31

36

14

1

ACK

BUSY

PE

SELECT

FLT

INPRIM

SELIN

ATFEED

STB

9

8

7

6

5

4

3

2

DI8

DI7

DI6

DI5

DI4

DI3

DI2

DI1

16

17

19

20

21

22

23

24

25

26

27

28

29

30

18

+5V

0V

0V

0V

0V

0V

0V

0V

0V

0V

0V

0V

0V

0V

0V

+5V

0V

Fig. 2.12

Fig. 2.12 shows the CDCC interface circuit.