II - 3

A2

A3

A4

A5

A6

A7

A8

A9

A1

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

31

32

56

55

54

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

34

33

A2

A3

A4

A5

A6

A7

A8

A9

A1

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

D2

D3

D4

D5

D6

D7

D8

D9

D1

D10

D11

D12

D13

D14

D15

D0

58

59

60

61

62

63

64

65

66

67

68

2

3

4

5

D2

D3

D4

D5

D6

D7

D8

D9

D1

D10

D11

D12

D13

D14

D15

D0

<08>

(

-11D)

(

-11B)

<02>

(02-08B)

(

-11D)

<07>

(

-11D) (02-09B)

(

-11B)

<01> (

-04C) (

-08B)

+5V

#2 MC68EC000FN16

NC 22

RESET

21

20

16

11

NC

RESET

HALT

CLK

DTACK

BR

BERR

AVEC

IPL0

IPL1

IPL2

IPL0

IPL1

IPL2

27

26

25

AVEC

+5V

SCLK

DTACK

BR

13

24

23

VCC

VCC

VCC

CND

CND

CND

CND

CND

BC

14

15

53

14

14

1

17

18

35

57

0V

12

30

29

28

19

7

10

8

9

FC0

FC1

FC2

MODE

A0

NC

AS

R/W

UDS

LDS

AS

R/W

UDS

LDS

FC0

FC1

FC2

BC

+5V

(

-04C)

(

-05F)

(

-05F)

(

-05F)

(

-04C)

(

-04C)

(

-04C)

(

-04C)

6

(

-05F)

(

-05E)

(

05)

(

-05F)

(

-05F)

(

-05F)

(

-05F)

(

-05F)

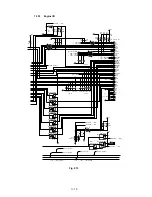

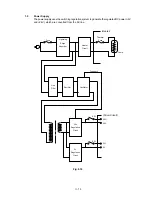

1.3

Main PCB

1.3.1

CPU

The CPU is a Motorola MC68EC000FN16 which is driven with a clock frequency of 15.3

MHz. This clock frequency is made by dividing the source clock of 30.67 MHz into two.

The address bus is 23 bits of A1 to A23, and the data bus is 16 bits. The total memory

space is 16 MBytes.

Fig. 2.3