RTX-24EM-HP

User guide

The technical characteristics can change without notice. AUR°EL S.p.A doesn’t assume the responsibility to the damages caused by an improper use of the device.

AUR°EL S.p.A.

Via Foro dei Tigli, 4 - 47015 Modigliana (FC) – ITALY 12/11/2019 - Rev. A

Tel.: +390546941124 – Fax: +390546941660 Page 32

http://www.aurel.it

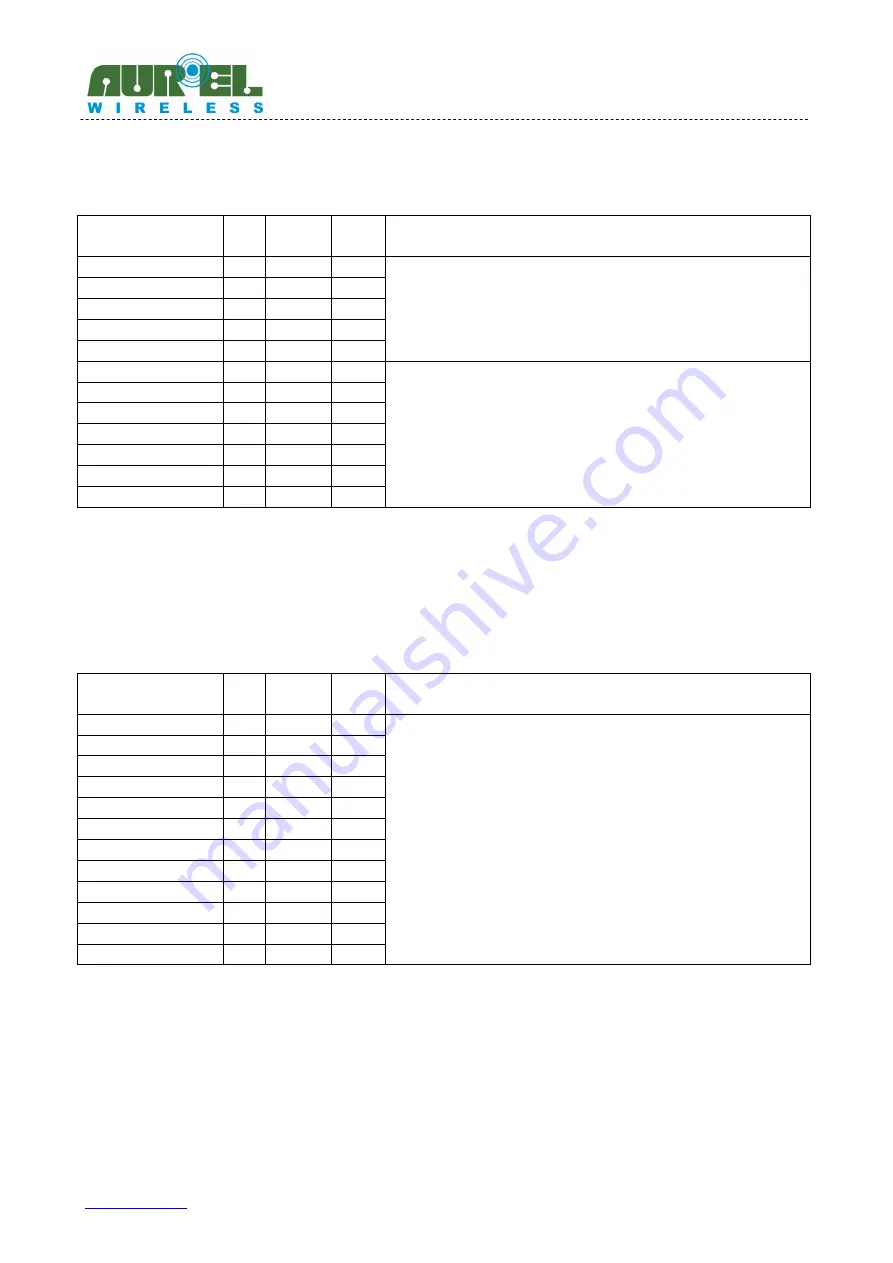

RAM2[11:0]@ Address 6

Bit

Default

Value

Reset

Value

Description

I_PA[4]

11

0

0

Current bias of the PA. Defines RF output in Transmit mode.

I_PA[3]

10

1

0

I_PA[2]

9

0

0

I_PA[1]

8

1

0

I_PA[0]

7

1

0

Reserved

6

0

0

Reserved.

Reserved

5

0

0

Reserved

4

0

0

Reserved

3

0

0

Reserved

2

0

0

Reserved

1

0

0

Reserved

0

0

0

RAM2[11:0]@ Address 7

Bit

Default

Value

Reset

Value

Description

Reserved

11

1

0

Reserved.

Reserved

10

0

0

Reserved

9

0

0

Reserved

8

1

0

Reserved

7

0

0

Reserved

6

0

0

Reserved

5

0

0

Reserved

4

0

0

Reserved

3

0

0

Reserved

2

0

0

Reserved

1

0

0

Reserved

0

0

0