MAX1000 User Guide

www.arrow.com

Page | 8

July 2017

2.2

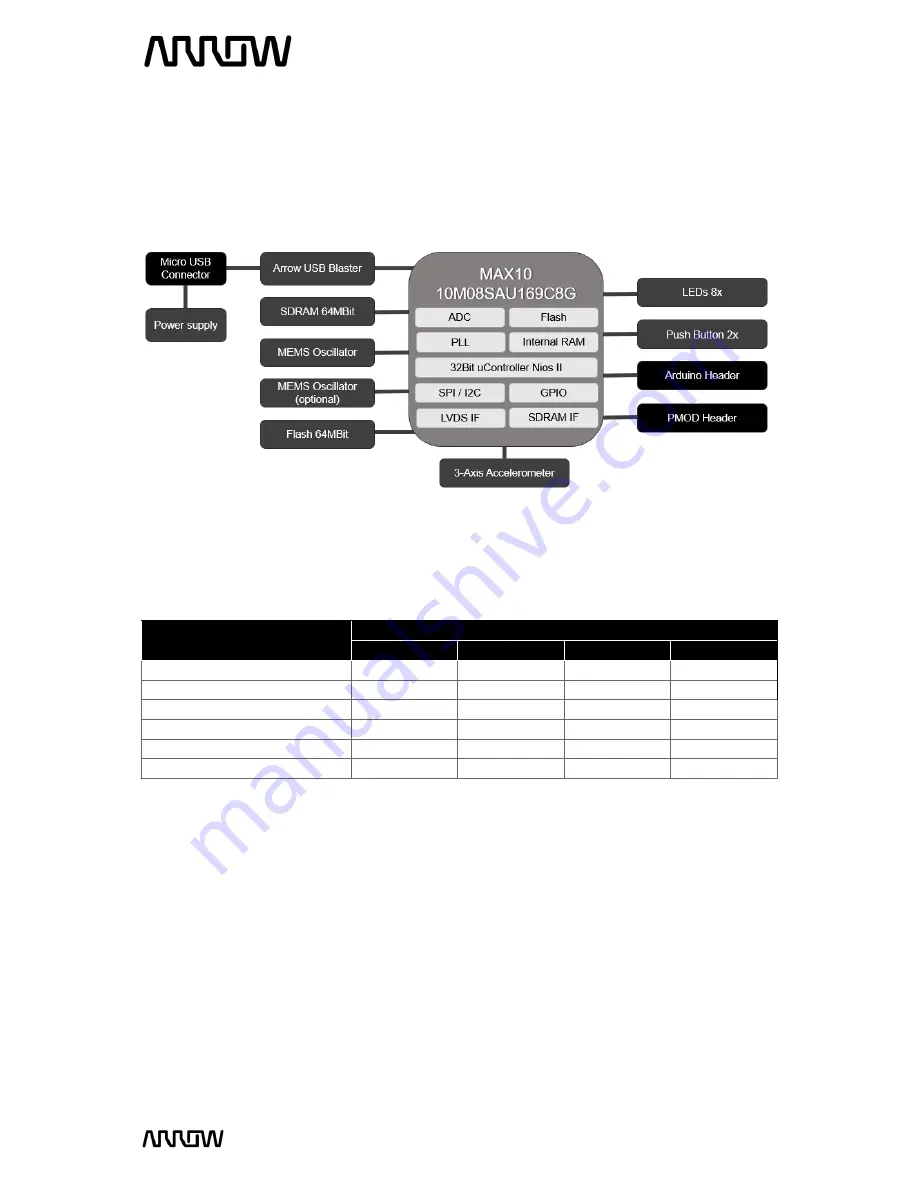

Block Diagram

Figure 2 represents the block diagram of the board. All the connections are established through

the MAX 10 FPGA device to provide maximum flexibility for users. Users can configure the FPGA

to implement any system design.

FPGA Device

Available MAX10 Devices for the MAX1000

Resources

Device

10M02

10M04

10M08

10M16

Logic Elements (LE) (K)

2

4

8

16

M9K Memory (K)

108

189

378

549

User Flash (K)

96

1248

1376

2368

Internal Configuration Image

1

2

2

2

ADC

-

1

1

1

PLLs

2

2

2

4

Configuration and Debug

On-board Arrow USB Programmer2 (mini-USB type B connector)

Memory Devices

64MBit to 128 MBit external flash memory

64MBit to 256 MBit external SDRAM memory

Figure 2 - MAX1000 Block Diagram