MAX1000 User Guide

www.arrow.com

Page | 14

July 2017

3.3.4

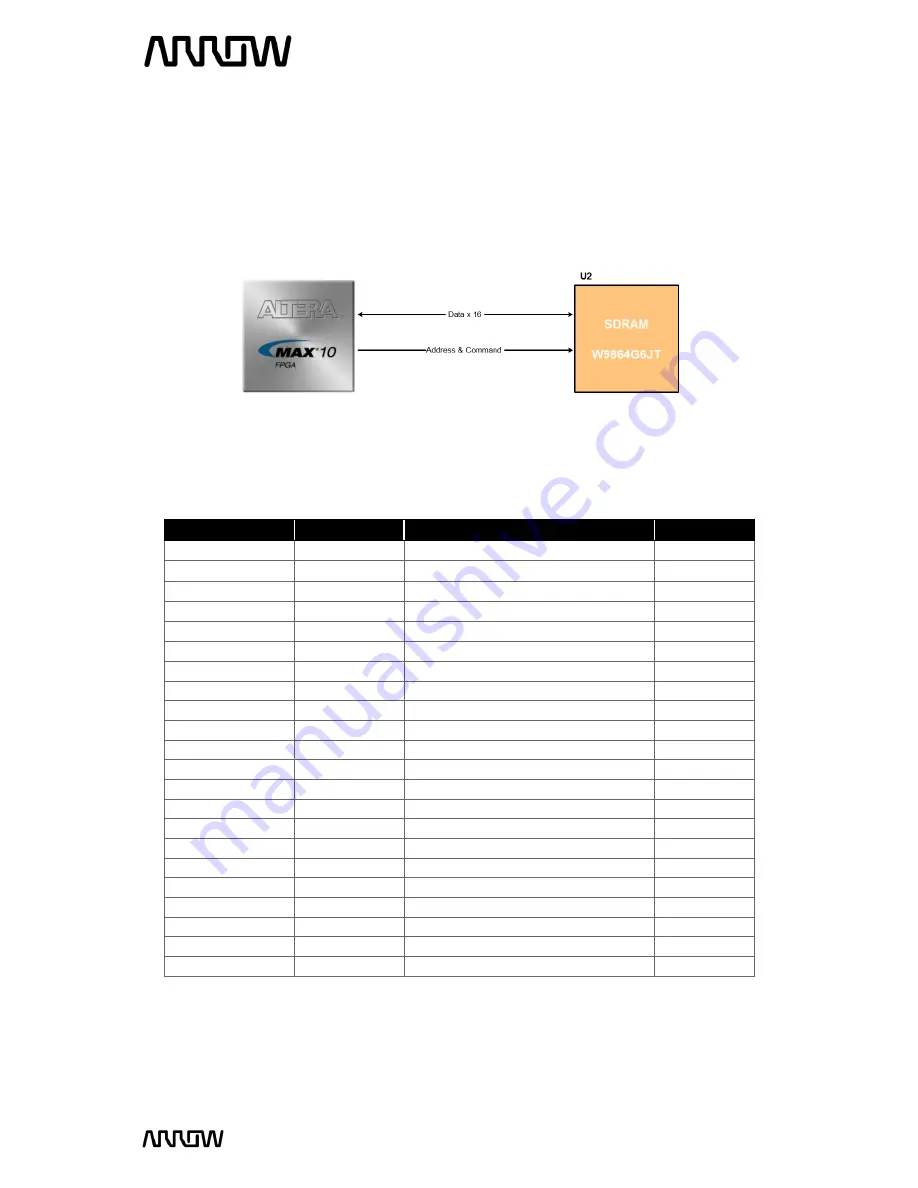

SDRAM Memory

The MAX1000 board supports 64 MBit (default version) or up to 256 MBit (customized version)

SDRAM which can operate up to 166 MHz clock frequency. Below are the connections and pinning

of the SDRAM used in the MAX1000.

Board Reference

FPGA Pin No.

Description

I/O Standard

A0

PIN_K6

SDRAM Address [0]

3.3 V

A1

PIN_M5

SDRAM Address [1]

3.3 V

A2

PIN_N5

SDRAM Address [2]

3.3 V

A3

PIN_J8

SDRAM Address [3]

3.3 V

A4

PIN_N10

SDRAM Address [4]

3.3 V

A5

PIN_M11

SDRAM Address [5]

3.3 V

A6

PIN_N9

SDRAM Address [6]

3.3 V

A7

PIN_L10

SDRAM Address [7]

3.3 V

A8

PIN_M13

SDRAM Address [8]

3.3 V

A9

PIN_N8

SDRAM Address [9]

3.3 V

A10

PIN_N4

SDRAM Address [10]

3.3 V

A11

PIN_M10

SDRAM Address [11]

3.3 V

A12

PIN_L11

SDRAM Address [12]

3.3 V

A13

PIN_M12

SDRAM Address [13]

3.3 V

BA0

PIN_N6

SDRAM Bank Address [0]

3.3 V

BA1

PIN_K8

SDRAM Bank Address [1]

3.3 V

CLK

PIN_M9

SDRAM Input Clock

3.3 V

CKE

PIN_M8

SDRAM Clock Enable

3.3 V

RAS

PIN_M7

SDRAM Row Address Strobe

3.3 V

CAS

PIN_N7

SDRAM Column Address Strobe

3.3 V

WE

PIN_K7

SDRAM Write Enable

3.3 V

CS

PIN_M4

SDRAM Chip Select

3.3 V

Figure 9 – SDRAM Connections