DE1-S

O

C C

OMPUTER

S

YSTEM WITH

N

IOS

II

For Quartus II 15.0

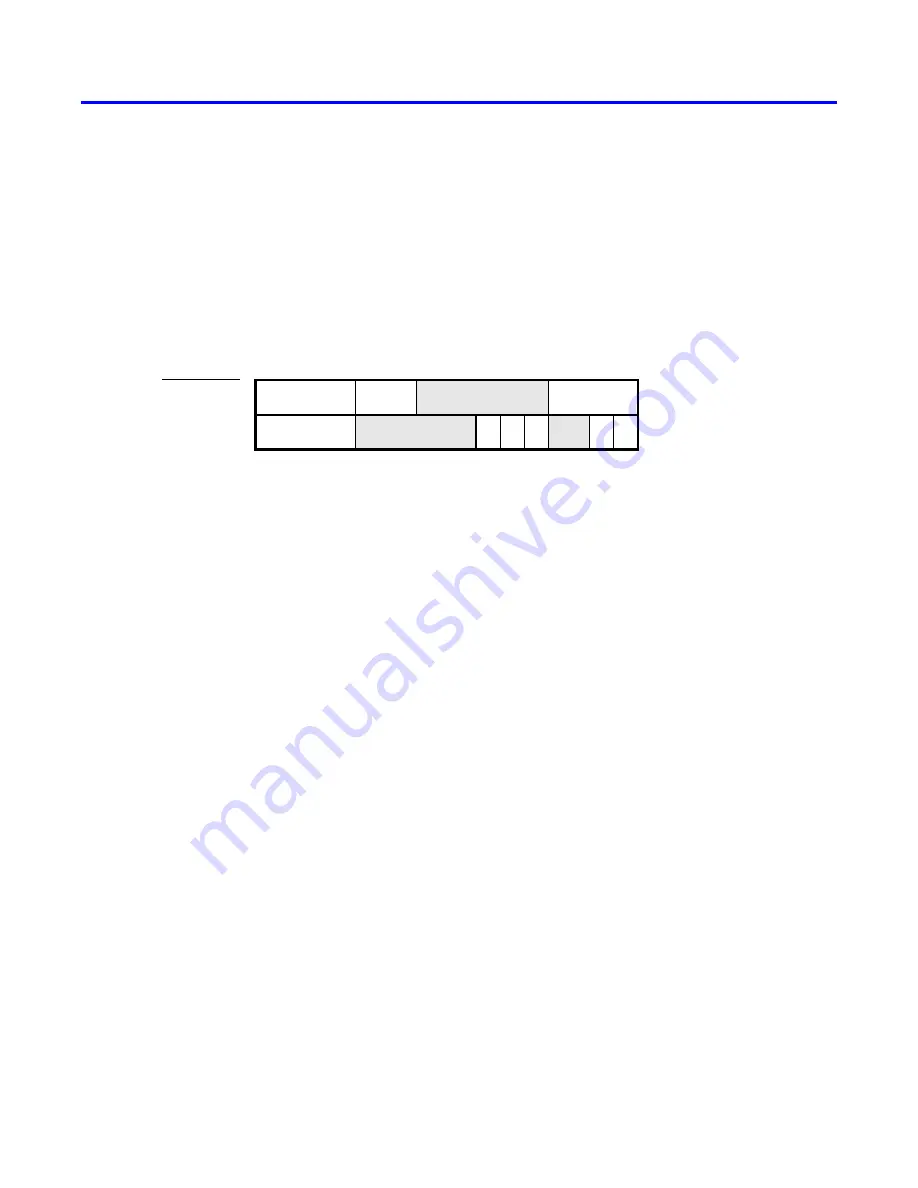

2.5

JTAG Port

The JTAG port implements a communication link between the DE1-SoC board and its host computer. This link

can be used by the Altera Quartus II software to transfer FPGA programming files into the DE1-SoC board, and

by the Altera Monitor Program, discussed in Section

8

. The JTAG port also includes a UART, which can be used

to transfer character data between the host computer and programs that are executing on the Nios II processor. If

the Altera Monitor Program is used on the host computer, then this character data is sent and received through its

Terminal Window

. The programming interface of the JTAG UART consists of two 32-bit registers, as shown in

Figure

10

. The register mapped to address

0xFF201000

is called the

Data

register and the register mapped to

address

0xFF201004

is called the

Control

register.

Address

0

7

31

16

. . .

0

x

FF201000

0

x

FF201004

DATA

RAVAIL

14

8

. . .

. . .

WSPACE

Unused

WI RI

WE RE

1

RVALID

AC

10 9

11

Unused

15

Data register

Control register

Figure 10. JTAG UART registers.

When character data from the host computer is received by the JTAG UART it is stored in a 64-character FIFO.

The number of characters currently stored in this FIFO is indicated in the field

RAVAIL

, which are bits 31

−

16 of the

Data

register. If the receive FIFO overflows, then additional data is lost. When data is present in the receive FIFO,

then the value of

RAVAIL

will be greater than 0 and the value of bit 15,

RVALID

, will be 1. Reading the character

at the head of the FIFO, which is provided in bits

7

−

0

, decrements the value of

RAVAIL

by one and returns this

decremented value as part of the read operation. If no data is present in the receive FIFO, then

RVALID

will be set

to 0 and the data in bits

7

−

0

is undefined.

The JTAG UART also includes a 64-character FIFO that stores data waiting to be transmitted to the host computer.

Character data is loaded into this FIFO by performing a write to bits 7

−

0 of the

Data

register in Figure

10

. Note

that writing into this register has no effect on received data. The amount of space,

WSPACE

, currently available in

the transmit FIFO is provided in bits 31

−

16 of the

Control

register. If the transmit FIFO is full, then any characters

written to the

Data

register will be lost.

Bit 10 in the

Control

register, called

AC

, has the value 1 if the JTAG UART has been accessed by the host computer.

This bit can be used to check if a working connection to the host computer has been established. The

AC

bit can be

cleared to 0 by writing a 1 into it.

The

Control

register bits

RE

,

WE

,

RI

, and

WI

are described in Section

3

.

2.5.1

Using the JTAG UART with Assembly Language Code and C Code

Figures

11

and

13

give simple examples of assembly language and C code, respectively, that use the JTAG UART.

Both versions of the code perform the same function, which is to first send an ASCII string to the JTAG UART, and

then enter an endless loop. In the loop, the code reads character data that has been received by the JTAG UART,

and echoes this data back to the UART for transmission. If the program is executed by using the Altera Monitor

Program, then any keyboard character that is typed into the

Terminal Window

of the Monitor Program will be echoed

Altera Corporation - University Program

2015

9