6

6. Tone Encoder

The CPU (IC9) is equipped with an internal tone encoder.The tone signal (67.0

to 250.3Hz) is output from pin 9 of the CPU to the varicap (D3) of the VCO for

modulation.

7. DCS Encoder

The CPU (IC9) is equipped with an internal DCS code encoder. The code (023

to 754) is output from pin 9 of the CPU to the varicap (D3) of the PLL reference

oscillator. When DCS is ON, DCS MUTE circuit (Q15-ON, Q18-ON, Q16-OFF)

works. The modulation activates in X1 side only.

8. CTCSS, DCS Decoder

The voice band of the AF output signal from pin 10 of IC5 is cut by sharp active

filter IC8 (VCVS) and amplified, then led to pin 4 of CPU. The input signal is

compared with the programmed tone frequency code in the CPU. The squelch

will open when they match.

9. Clock Shift

In the unlikely event that CPU clock noise is present on a particular operating

frequency programmed into the radio, you can shift the CPU clock frequency to

avoid the CPU clock-noise. The output signal from pin 31 of the CPU turns on

Q30. Then the oscillation frequency of X2 will be shifted about 300 ppm.

5) M3826M8L

***

GP (XA0644)

CPU

Terminal Connection

(TOP VIEW)

Summary of Contents for DJ-195

Page 2: ......

Page 11: ...10 3 M5222FP 600C XA0385 Electronic Volume ...

Page 12: ...11 4 TK14521MTL XA0515 IF System ...

Page 14: ...13 8 S 81250SG QD T1 XA0619 Top View 9 S 80845ALMP EA9 T2 XA0620 Voltage Regulator ...

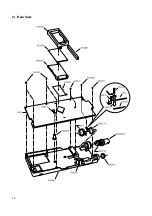

Page 16: ...15 EXPLODED VIEW 1 Front View www ALIMCO ru ...

Page 17: ...16 2 Rear View ...

Page 28: ......

Page 29: ...27 PC BOARD VIEW MAIN SIDE A MAIN Side B ...

Page 30: ...28 SCHEMATIC DIAGRAM ...

Page 31: ...29 BLOCK DIAGRAM www ALIMCO ru ...

Page 32: ......

Page 33: ......