SERIES IP521 INDUSTRIAL I/O PACK EIA/TIA-422B SERIAL COMMUNICATION MODULE

___________________________________________________________________________________________

- 14 -

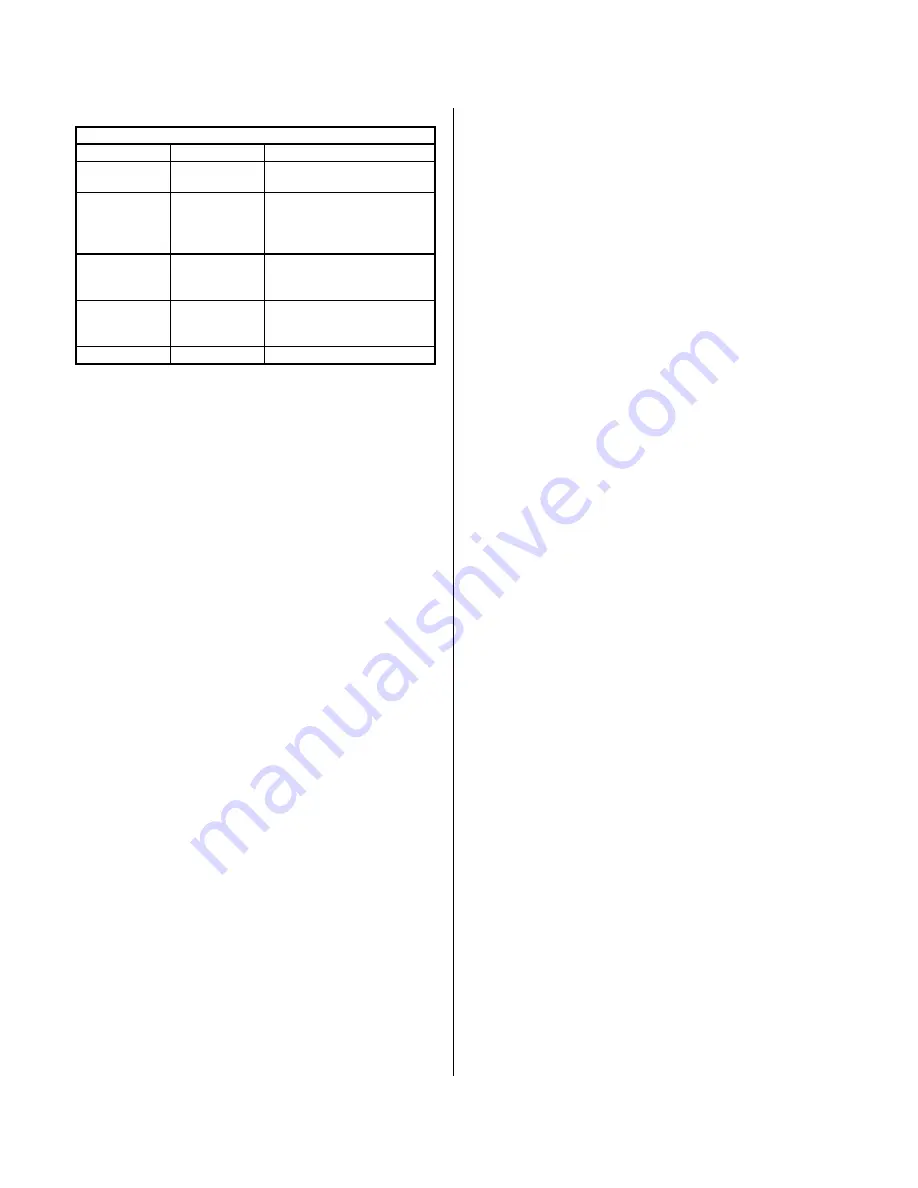

SIGNALS (INTERNAL & EXTERNAL):

TxD

Reset

High

Interrupt

(RCVR errors)

Read LSR/

Reset

Low

Interrupt

(RCVR data

ready)

Read RCVR

Buffer

Register/

Reset

Low

Interrupt

(THRE)

Read

ISR/Write

THR/Reset

Low

Interrupt

(Modem Status

Changes)

Read MSR/

Reset

Low

RTS*

Reset

High

IP521 PROGRAMMING CONSIDERATIONS

Each serial channel of this module is programmed by the control

registers: LCR, IER, DLL, DLM, MCR, and FCR. These control

words define the character length, number of stop bits, parity, baud

rate, and modem interface. The control registers can be written in

any order, but the IER register should be written last since it controls

the interrupt enables. The contents of these registers can be

updated any time the serial channel is not transmitting or receiving

data.

The complete status of each channel can be read by the host

CPU at any time during operation. Two registers are used to report

the status of a particular channel: the Line Status Register (LSR)

and the Modem Status Register (MSR).

Serial channel data is read from the Receiver Buffer Register

(RBR), and written to the Transmitter Holding Register (THR).

Writing data to the THR initiates the parallel-to-serial transmitter shift

register to the TxD line. Likewise, input data is shifted from the RxD

pin to the Receiver Buffer Register as it is received.

The Scratch Pad Register is used to store the interrupt vector

for the port. In response to an interrupt select cycle, the IP module

will provide a read of this port. As such, each port may have a

unique interrupt vector assigned. Interrupts are served in a shifting-

priority fashion as a function of the last interrupting port serviced to

prevent continuous interrupts from a higher-priority interrupt channel

from freezing out service of a lower priority channel.

This board operates in two different modes. In one mode, this

device remains software compatible with the industry standard

16C450 family of UART’s, and provides double-buffering of data

registers. In the FIFO Mode (enabled via bit 0 of the FCR register),

data registers are FIFO-buffered so that read and write operations

can be performed while the UART is performing serial-to-parallel

and parallel-to-serial conversions.

Two FIFO modes of operation are possible: FIFO Interrupt

Mode and FIFO Polled Mode. In FIFO Interrupt Mode, data transfer

is initiated by reaching a pre-determined trigger-level or generating

time-out conditions. In FIFO-Polled Mode, there is no time-out

condition indicated or trigger-level reached. The transmit and the

receive FIFO’s simply hold characters and the Line Status Register

must be read to determine the channel status.

To make programming and communicating with the board

easier, Acromag provides you with the Industrial I/O Pack Software

Library diskette. The functions provided are written in the “C”

programming language and can be linked into your application.

Refer to the “README.TXT” file in the root directory and the

“INFO521.TXT” file in the “IP521” subdirectory on the diskette for

details.

Acromag also provides a software diskette of IP module Object

Linking and Embedding (OLE) drivers for Windows 95

/NT

compatible application programs (Model IPSW-OLE-PCI, MSDOS

format). This software provides individual drivers that allow all IP

modules and the APC8620 carrier to be easily integrated into

Windows

application programs, such as Visual C++

, Visual

Basic

, Borland Delphi

, Microsoft

Office

97 applications and

others. The OLE controls provide a high-level interface to IP

modules, eliminating the need to perform low-level reads/writes of

registers, and the writing of interrupt handlers—all the complicated

details of programming are handled by the OLE controls. These

functions are intended for use in conjunction with an Acromag

personal computer carrier and consist of a carrier OLE control, and

an OLE control for each Acromag IP module as well as a generic

OLE control for non-Acromag IP modules.

In addition, Acromag provides a software product (sold

separately) consisting of IP module VxWorks

drivers. This

software (Model IPSW-API-VXW MSDOS format) is composed of

VxWorks

(real time operating system) libraries for all Acromag IP

modules and carriers including the AVME9660/9630, APC8610, and

APC8620. The software is implemented as a library of “C” functions

which when linked with existing user code makes possible simple

control of all Acromag IP modules and carriers.

FIFO Polled-Mode

Resetting all Interrupt Enable Register (IER) bits to 0, with FIFO

Control Register (FCR) Bit 0 =1, puts the channel into the polled-

mode of operation. The receiver and transmitter are controlled

separately and either one or both may be in the polled mode. In

FIFO-Polled Mode, there is no time-out condition indicated or trigger-

level reached, the transmit and the receive FIFO’s simply hold

characters and the Line Status Register must be read to determine

the channel status.

FIFO-Interrupt Mode

In FIFO Interrupt Mode, data transfer is initiated by reaching a

pre-determined trigger-level or generating a time-out condition.

Please note the following with respect to this mode of operation.

When the receiver FIFO and receiver interrupts are enabled, the

following receiver status conditions apply:

1. LSR Bit 0 is set to 1 when a character is transferred from the

shift register to the receiver FIFO. It is reset to 0 when the FIFO

is empty.

2. The receiver line-status interrupt (ISR=06) has a higher priority

than the received data-available interrupt (ISR=04).

3. The receive data-available interrupt is issued to the CPU when

the programmed trigger level is reached by the FIFO. It is

cleared when the FIFO drops below its programmed trigger

level. The receive data-available interrupt indication (ISR=04)

also occurs when the FIFO reaches its trigger level, and is

cleared when the FIFO drops below its trigger level.