AD824

14

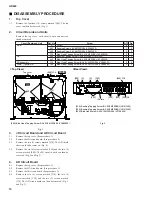

LSI PIN DESCRIPTION

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCK

Vss

TC

DIM1

DIM0

DOM1

DOM0

KM1

I

O

O

O

O

O

O

O

O

O

I

I

O

O

O

O

I

I

I

I

I

Auxiliary input for audio data

Asynchronous buffer operation flag

Audio data output

Parity flag output

Fs x 1 Synchronous output signal for DAC

Fs x 1 Synchronous output signal for DSP

Fs x 64 Bit clock output

Fs x 1 Word clock output

Fs x 128 Bit clock output

Fs x 256 Bit clock output

Clock synchronization control input

Crystal oscillator connection or external

clock input

Crystal oscillator connection

VCO oscillating clock connection

PLL lock flag

Logic section power (GND)

PLL time constant switching output

Data input mode selection

Data input mode selection

Data output mode selection

Data output mode selection

Clock mode switching input 1

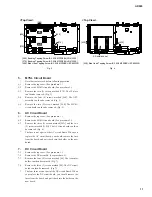

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

RSTN

Vdda

CTLN

PCO

(NC)

CTLP

Vssa

TSTN

KM2

KM0

FS1

FS0

CSM

EXTW

DDIN

LR

Vdd

ERR

EMP

CD0

CCK

CLD

I

I

O

I

I

I

I

O

O

I

I

I

O

O

O

O

I

I

System reset input

VCO section power (+5 V)

VCO control input N

PLL phase comparison output

VCO control input P

VCO section power (GND)

Test terminal. Open for normal use

Clock mode switching input 2

Clock mode switching input 0

Channel status sampling frequency

display output 1

Channel status sampling frequency

display output 0

Channel status output method selection

External synchronous auxiliary input

word clock

EIAJ (AES/EBU) data input

PLL word clock output

Logic section power (+5 V)

Data error flag output

Channel status emphasis control code

output

3-wire type microcomputer interface data

output

3-wire type microcomputer interface clock

input

3-wire type microcomputer interface load

input

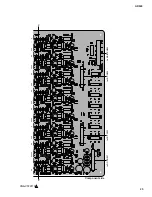

YM3436DK (XG948E0) DIR2 (Digital Format Interface Receiver)

MAIN: IC921, 922

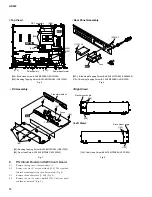

PIN

NO.

I/O

FUNCTION

NAME

PIN

NO.

I/O

FUNCTION

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VREFL

GNDL

VCOML

AINL+

AINL-

ZCAL

VD

DGND

CAL

/RST

SMODE2

SMODE1

LRCK

SCLK

O

-

O

I

-

I

-

-

O

I

I

I

I/O

I/O

L ch standard voltage output (+3.75 V)

L ch Ground

L ch common voltage (+2.5 V)

L ch analog (+) input

L ch analog (-) input

Zero calibration

“L”: VCOML,VCOMR

“H”: Analog input (AINL+/-,AINRR+/-)

Power supply for digital

Ground for digital

Calibration status

Reset

Serial interface mode select

MSB first, 2’s compliment

L/R ch select clock

Serial data clock

15

16

17

18

19

20

21

22

23

24

25

26

27

28

SDATA

FSYNC

MCLK

CMODE

HPFE

TEST

BGND

AGND

VA

AINR-

AINR+

VCOMR

GNDR

VREFR

O

I/O

I

I

I

I

-

-

-

I

I

O

-

O

Serial data output

Frame synchronization clock

Master clock input

CMODE=“H”:384 fs

CMODE=“L”:256 fs

Master clock select

“L”: MCLK=256 fs (12.288 MHz @fs=48 kHz)

“H”: MCLK=384 fs (18.432 MHz @fs=48 kHz)

HPF enable “L”: OFF “H”: ON

TEST pin

Connect it with DGND.

Ground

Ground for analog

Power supply for analog (+5 V)

R ch analog (+) input

R ch analog (-) input

R ch common voltage (-2.5 V)

R ch ground

R ch standard voltage output (+3.75 V)

AK5392-VS-E2 (XV065A00) ADC (Analog to Digital Converter)

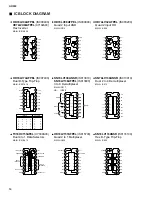

SMODE2

L

L

H

H

SMODE1

L

H

L

H

MODE

Slave mode

Master mode

Slave mode

Master mode

LRCK

H/L

H/L

L/H

L/H

AD: IC105, 305, 505, 705

Содержание AD824

Страница 22: ...MAIN Circuit Board B B 3NA V579130 AD824 22 ...

Страница 23: ...E B B MAIN MYSL 3NA V579130 MYSL Circuit Board AD824 23 Pattern side Pattern side ...

Страница 24: ...3NA V579110 INPUT BAL 1 2 3 4 5 6 7 8 1 HA Circuit Board C C AD824 24 ...

Страница 25: ...AD824 25 3NA V579110 to MAIN CN903 1 C C to JK CN202 to JK CN102 to DC CN007 Component side ...

Страница 26: ...HA Circuit Board 3NA V579110 1 D D AD824 26 ...

Страница 27: ...3NA V579110 1 D D AD824 27 Pattern side ...

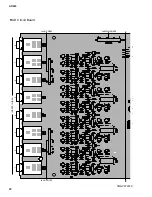

Страница 28: ...AD824 28 3NA V579120 AD Circuit Board E E INSERT IN BAL to MAIN CN909 1 2 3 4 5 6 7 8 to JK CN203 to JK CN103 ...

Страница 30: ...AD824 30 AD Circuit Board 3NA V579120 F F ...

Страница 31: ...AD824 31 JK Circuit Board F F AD JK 3NA V579120 Pattern side Pattern side ...

Страница 33: ...PN Circuit Board 3NA V579100 1 H H H H AD824 33 Pattern side ...