40

www.xilinx.com

Ethernet 1000BASE-X PCS/PMA or SGMII v7.0

UG145 January 18, 2006

Chapter 4:

Detailed Example Design

R

Changing Frame Error Status

Errors can be inserted into any of the predefined frames in any position by setting the

“error” field to ‘1’ in any column of that frame. Injected errors are automatically updated in

both stimulus and monitor functions.

Changing the Core Configuration

The configuration of the Ethernet 1000BASE-X PCS/PMA core used in the demonstration

test bench can be altered.

Caution

:

Certain configurations of the core can cause the test bench to fail, or to cause processes

to run indefinitely. For example, the demonstration test bench will not auto-negotiate with the design

example. Determine the configurations that can safely be used with the test bench

.

If the MDIO interface option has been selected, the core can be reconfigured by editing the

injected MDIO frame in the demonstration test bench. See the

Xilinx LogiCORE Ethernet

1000BASE-X PCS/PMA or SGMII User Guide

for more information about using the MDIO

interface.

If the MDIO interface option has not been selected, the core can be reconfigured by

modifying the configuration vector directly. See the

Xilinx LogiCORE Ethernet 1000BASE-X

PCS/PMA or SGMII User Guide

for information about using the configuration vector.

SGMII Example Design / Dynamic Switching Example Design

Note:

This is the example design provided when the core is generated for the SGMII standard; it is

also provided when the core is generated with the 1000BASE-X/SGMII dynamic switching capability.

Example Design Top-Level HDL

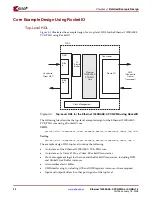

Figure 4-7

illustrates an example design for top-level HDL for the Ethernet 1000BASE-X

PCS/PMA or SGMII LogiCORE in SGMII mode.

The top-level example design for the Ethernet 1000BASE-X PCS/PMA core in SGMII mode

is described in the following files:

Figure 4-7:

Top- Level HDL for the Ethernet 1000BASE-X PCS/PMA or SGMII

LogiCORE in SGMII mode

Ethernet

1000BASE-X

PCS/PMA

Core

(SGMII mode)

FPGA

RocketIO

Transceiver

GMII

IOBs

In

IOBs

Out

SGMII

Adaptation

Module

Clock Management

Connect to

Client MAC

Serial GMII

(SGMII)

Содержание LogiCORE

Страница 1: ...R LogiCORE Ethernet 1000BASE X PCS PMA or SGMII v7 0 Getting Started Guide UG145 January 18 2006...

Страница 4: ...www xilinx com Ethernet 1000BASE X PCS PMA or SGMII v7 0 UG145 January 18 2006...

Страница 8: ...8 www xilinx com Ethernet 1000BASE X PCS PMA or SGMII v7 0 UG145 January 18 2006 R...

Страница 12: ...12 www xilinx com Ethernet 1000BASE X PCS PMA or SGMII v7 0 UG145 January 18 2006 Preface About This Guide R...