W632GG6KB

Publication Release Date: Jan. 03, 2017

Revision: A06

- 24 -

8.3.4

Mode Register MR3

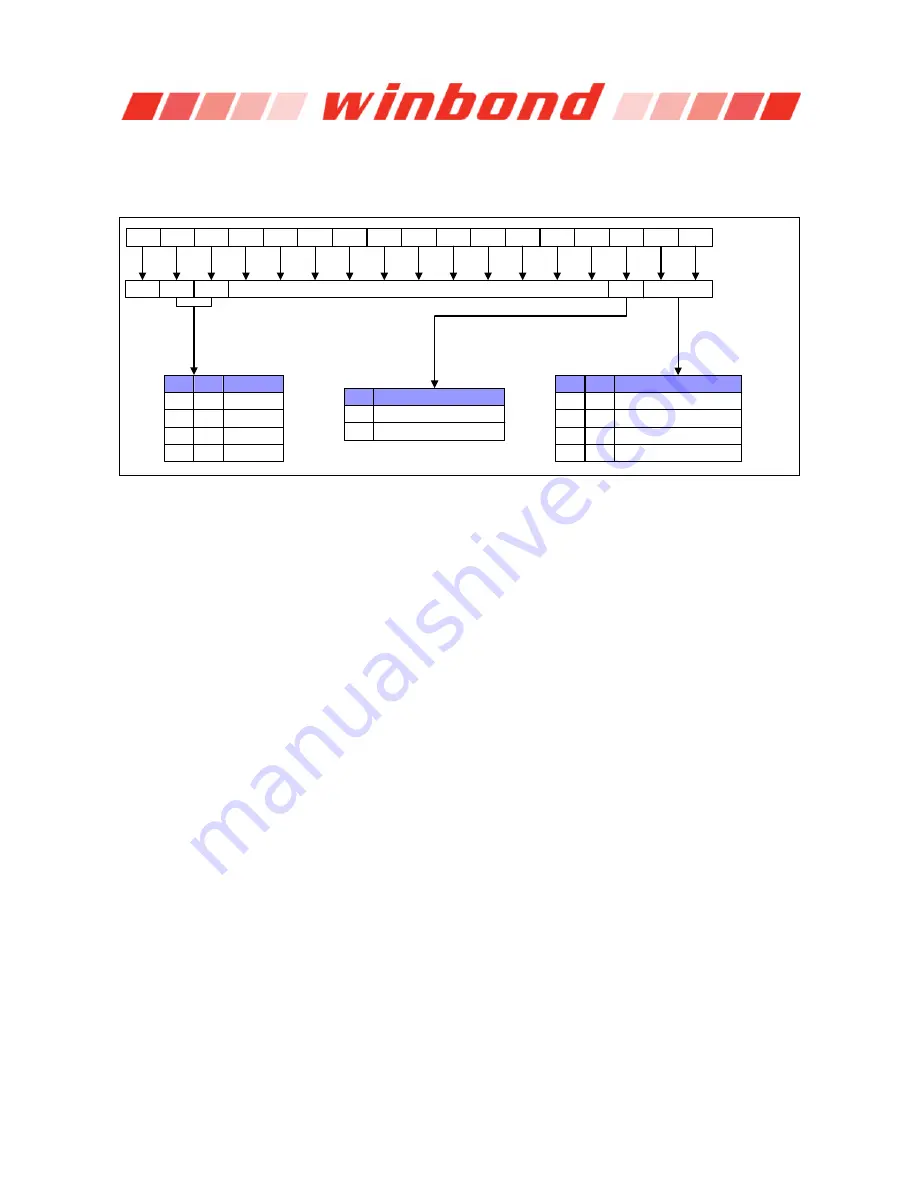

The Mode Register MR3 controls Multi purpose registers. The Mode Register 3 is written by asserting

low on CS#, RAS#, CAS#, WE#, high on BA1 and BA0, and low on BA2 while controlling the states of

address pins according to the Figure 8 below.

BA1

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

Address Field

Mode Register 3

BA1

BA0

MR Select

0

0

0

0

1

1

1

1

MR0

MR1

MR2

MR3

Dataflow from MPR

Normal operation

*3

BA0

A13

1

1

MPR Loc

MPR

0*

1

MPR Operation

A1

A0

0

0

0

0

1

1

1

1

Predefined pattern

*2

RFU

RFU

RFU

MPR Address

BA2

0*

1

A2

0

1

MPR

MR Select

MPR location

Notes:

1. BA2, A3~A13 are reserved for future use and must be programmed to

“0” during MRS.

2. The predefined pattern will be used for read synchronization.

3. When MPR control is set for normal operation (MR3 A[2] = 0) then MR3 A[1:0] will be ignored.

Figure 8

– MR3 Definition

8.3.4.1

Multi Purpose Register (MPR)

The Multi Purpose Register (MPR) function is used to Read out a predefined system timing calibration

bit sequence. To enable the MPR, a MODE Register Set (MRS) command must be issued to MR3

Register with bit A2 = 1. Prior to issuing the MRS command, all banks must be in the idle state (all

banks precharged and t

RP

met). Once the MPR is enabled, any subsequent RD or RDA commands

will be redirected to the Multi Purpose Register. When the MPR is enabled, only RD or RDA

commands are allowed until a subsequent MRS command is issued with the MPR disabled (MR3 bit

A2 = 0). Power Down mode, Self Refresh, and any other non-RD/RDA command is not allowed during

MPR enable mode. The RESET function is supported during MPR enable mode. For detailed MPR

operation refer to section 8.10

on page 34.