3 Hardware Configuration

This section describes the various portions of the TSW14J58EVM hardware.

3.1 Power Connections

The TSW14J58EVM hardware is designed to operate from a single supply voltage of +5.5 V DC. The power

input is controlled by the on and off switch, SW5. Make sure this switch is in the off position before inserting

the provided power cable. Insert the connector end of the power cable into J2 of the EVM. Connect the positive

red wire end of the power cable to +5.5 V DC output of a power supply rated for at least 5 Amps. Connect

the negative black wire to the RETURN or GND of the power supply. The board can also be powered up by

pro5.5 V DC to the red test point, TP18, and the return to any black GND test point. As an example, the

TSW14J58 draws approximately 0.6 A at power-up and 3 A when capturing 8 lanes of data from an AFE at a line

rate of 24.33 Gpbs.

Note

The typical power supply range for the TSW14J58EVM is 5.5V with a power consumption of about

16.5W. It is recommended that at least a 5 A rated supply be provided to the TSW14J58EVM due to

the current consumption increase when data is being captured by HSDC Pro.

3.2 Switches, Jumpers, and LEDs

3.2.1 Switches and Push-Buttons

The TSW14J58 contains several switches and push-buttons that enable certain functions on the board. The

description of the switches is found in

.

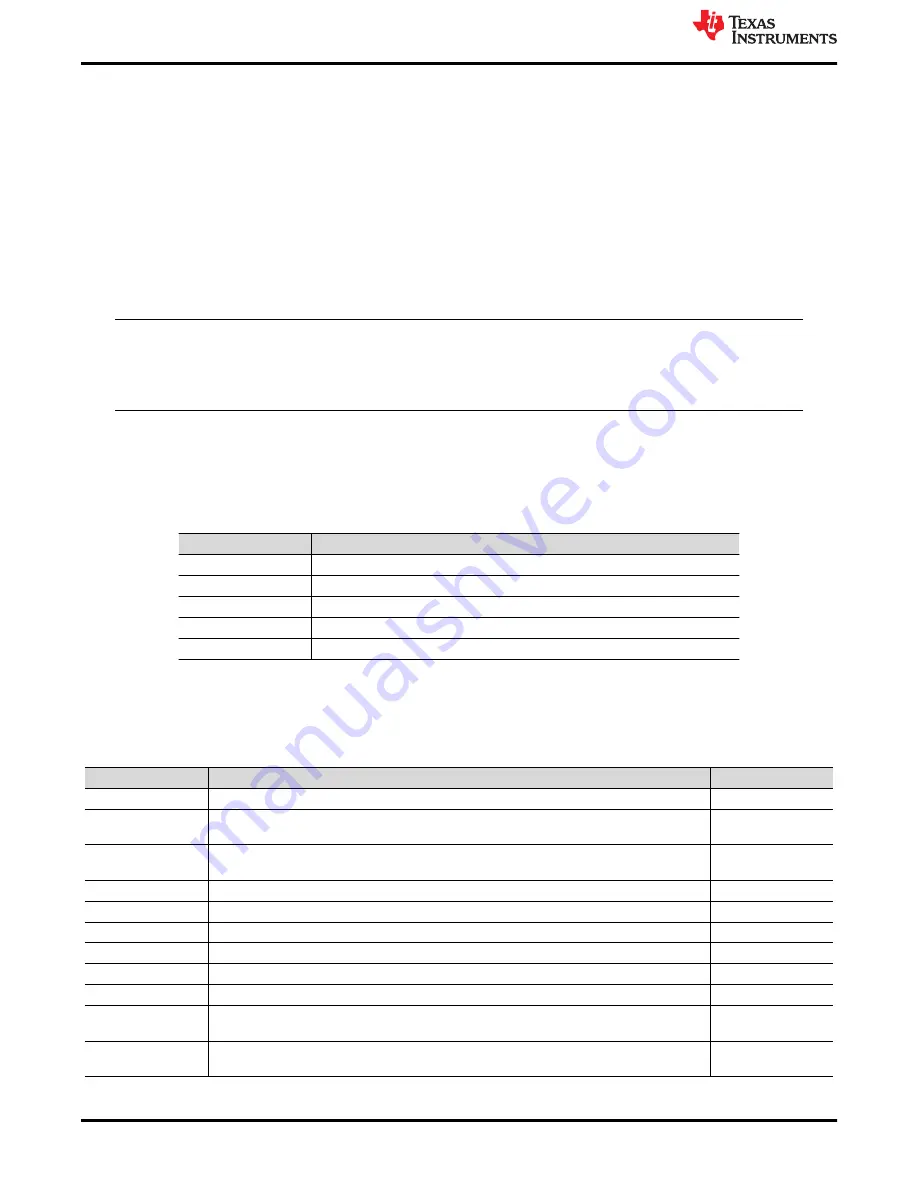

Table 3-1. Switch Description of the TSW14J58 Device

Component

Description

SW1

USB 2.0 reset

SW2

USB 3.0 reset

SW3

FPGA hardware reset

SW4

Force FPGA firmware load from selected EEPROM

SW5

Board main power switch

3.2.2 Jumpers

The TSW14J58 contains several jumpers (JP) and solder jumpers (SJP) that enable certain functions on the

board. The description of the jumpers is found in

Table 3-2. Jumper Description of the TSW14J58 Device

Component

Description

Default

J4

Disables VCCO_3V3 supply when installed

Open

J5

USB3.0 GPIO0 configuration. With shunt on pins 1–2, sets this high. Shunt on 2–3 sets this

low

Open

J6

USB3.0 GPIO1 configuration. With shunt on pins 1–2, sets this high. Shunt on 2–3 sets this

low

Open

J10

Disables VCCO_1V2 supply when installed

Open

J11

Disables VCCO_1V8 supply when installed

Open

J15

Disables MGTAVCC_0V9 supply when installed

Open

J16

Disables MGTAVTT_1V2 supply when installed

Open

J17

Disables MGTAVCCAUX_1V2 supply when installed

Open

J19

Disables VCCO_2V5 supply when installed

Open

J21

Output SYNCA/B/C and input TRIG_IN translator voltage level select. With shunt on pins

1–2, voltage is 3.3V. With shunt on pins 2–3, voltage is controlled by TP30.

1 to 2

J28

Buffers U38, U44, U46 enable. With shunt on pins 1–2, U44 is enabled and U38 and U46 are

disabled. With shunt on pins 2–3, U44 is disabled and U38 and U46 are enabled.

1 to 2

Hardware Configuration

6

TSW14J58 JESD204C Data Capture and

Pattern Generator Card

SLWU094 – MARCH 2021

Copyright © 2021 Texas Instruments Incorporated