SLUU131A – September 2002 – Revised February 2003

10

TPS40001 Based Converter Delivers 10-A Output

5

PowerPAD Packaging

The TPS4000X family is available in the DGQ version of TI’s PowerPAD

t

thermally enhanced package. In the

PowerPAD

t

, a thermally conductive epoxy is utilized to attach the integrated circuit die to the leadframe die

pad, which is exposed on the bottom of the completed package. The leadframe die pad can be soldered to the

PCB using standard solder flow techniques when maximum heat dissipation is required. However, depending

on power dissipation requirements, the PowerPAD

t

may not need to soldered to the PCB.

The thermally conductive epoxy bonding the circuit die to the leadframe die pad causes a high resistance from

the leadframe die pad to the device ground pin 5. When the PowerPad

t

package is soldered to the PCB, the

leadframe die pad can be connected to ground (pin 5), but this is not required. The leadframe die pad should

not be connected to other potentials in the circuit.

The PowerPAD

t

package helps to keep the junction temperature rise relatively low even with the power

dissipation inherent in the onboard MOSFET drivers. This power loss is proportional to switching frequency,

drive voltage, and the gate charge needed to enhance the N-channel MOSFETs. Effective heat removal allows

the use of ultra small packaging while maintaining high component reliability.

To effectively remove heat from the PowerPAD

t

package, a thermal land should be provided directly

underneath the package. This thermal land usually has vias that help to spread heat to internal copper layers

and/or the opposite side of the PCB. The vias should not have thermal reliefs that are often used on ground

planes, because this reduces the copper area to transfer heat. Additionally, the vias should be small enough

so that the holes are effectively plugged when plated. This prevents the solder from wicking away from the

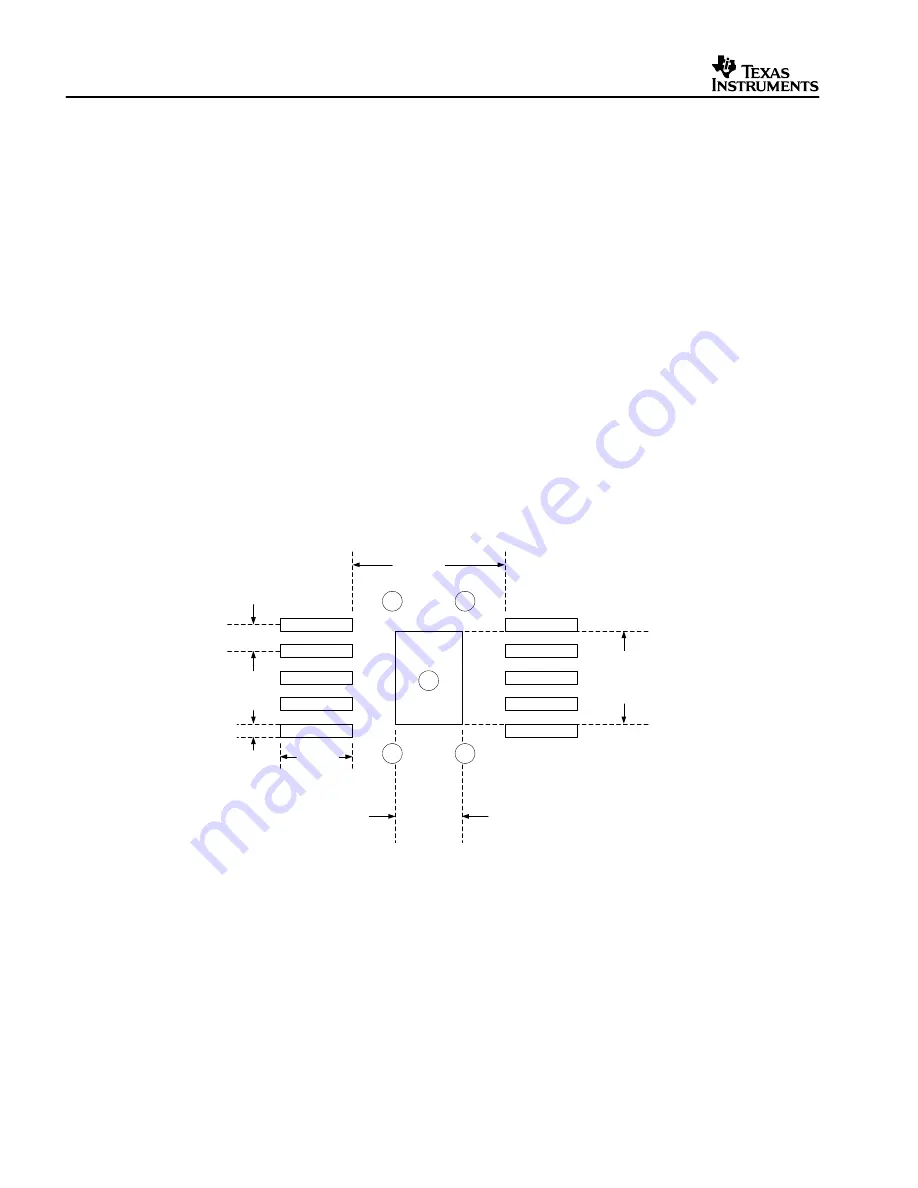

connection between the PCB surface and the bottom of the part. A typical footprint pattern is shown in Figure 2,

but does not include the additional copper plane which includes the vias above and below the device.

2.92mm

(0.115”)

0.5mm

(0.0197”)

0.28mm

(0.011”)

1.40mm

(0.055”)

Via Dia.

0.33mm

(0.013”)

Miminum

PowerPad ”X”

1.3mm

(0.050”)

Minimum

PowerPad ”Y”

1.7mm

(0.068”)

Figure 3. PowerPAD

t

PCB Layout Guidelines

The Texas Instrument document, PowerPAD

t

Thermally Enhanced Package Application Report (Texas

Instrument Literature Number SLMA002) should be consulted for more information on the PowerPAD

t

package. This report offers in-depth information on the package, assembly and rework techniques, and

illustrative examples of the thermal performance of the PowerPAD

t

package.