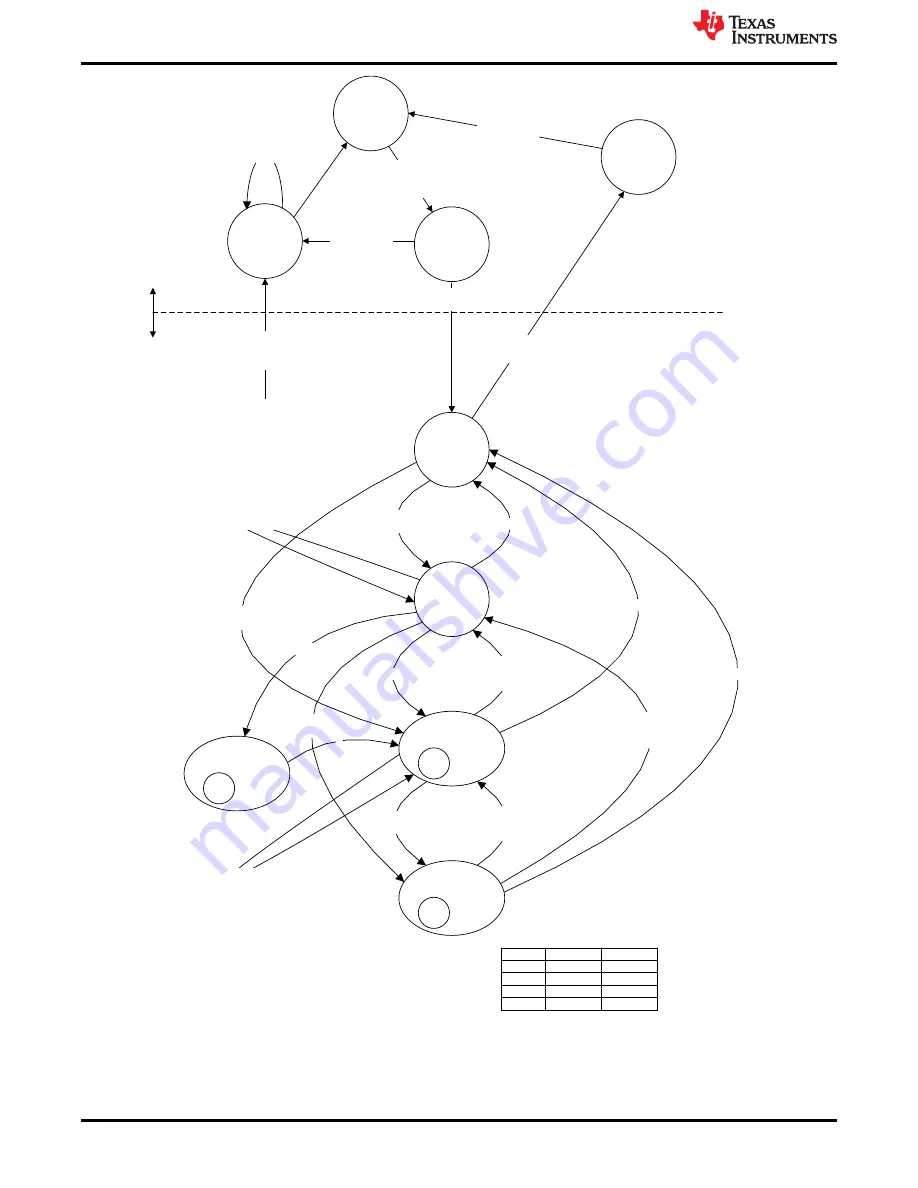

INIT

BOOT BIST

SAFE

RECOVERY

FSM

PFSM

STANDBY

INIT Complete

No Errors

No Residual Voltage

BOOT BIST

Error

BOOT BIST

Success

Recovery Count

Threshold

LP_STANDBY

MCU Only

ACTIVE

LP_STANDBY_SEL

=1

MCU Power Error

Immediate Shutdown

Orderly Shutdown

A

Trigger

NSLEEP2

NSLEEP1

1

1

B

1

0

C

0

1

D

0

0

Valid On Request

STARTUP_DEST[1:0] = 11b

Off Request

B

A or WKUP1 or

Valid On Request

STARTUP_DEST[1:0] = 11b

C or

D

B or WKUP2 or

Valid On Request

STARTUP_DEST[1:0] = 10b

Valid On Request

STARTUP_DEST[1:0] = 10b

OFF Request

C or

D

A or WKUP1 or

Valid On Request

STARTUP_DEST[1:0] = 11b

OFF Request

Warm Reset triggered by

ESM SOC or

WatchDog Error

Warm Reset triggered by

MCU SOC or

WatchDog Error

DDR

Retention

DDR

From any PFSM State

Valid Wake

Request

Pwr SOC Error

DDR

SOC Power Error

B

Figure 6-1. Pre-Configurable Finite State Machine (PFSM) Mission States and Transitions

When the PMICs transition from the FSM to the PFSM, several initialization instructions are performed to disable

the residual voltage checks on both the BUCK and LDO regulators, set the FIRST_STARTUP_DONE bit and

Pre-Configurable Finite State Machine (PFSM) Settings

32

Optimized Dual TPS6594-Q1 PMIC User Guide for Jacinto

™

7 DRA829 or

TDA4VM Automotive PDN-0C

SLVUC99 – JANUARY 2022

Copyright © 2022 Texas Instruments Incorporated