Optional Signal Conditioning Op-Amp (U8B)

3-5

EVM Operation

In unity gain, the OPA627 op-amp, U2, performs very well with very large

capacitive loads. Increasing the gain enhances the amplifier’s ability to drive

even more capacitance, and adding a load resistor would even improve the

capacitive load drive capability.

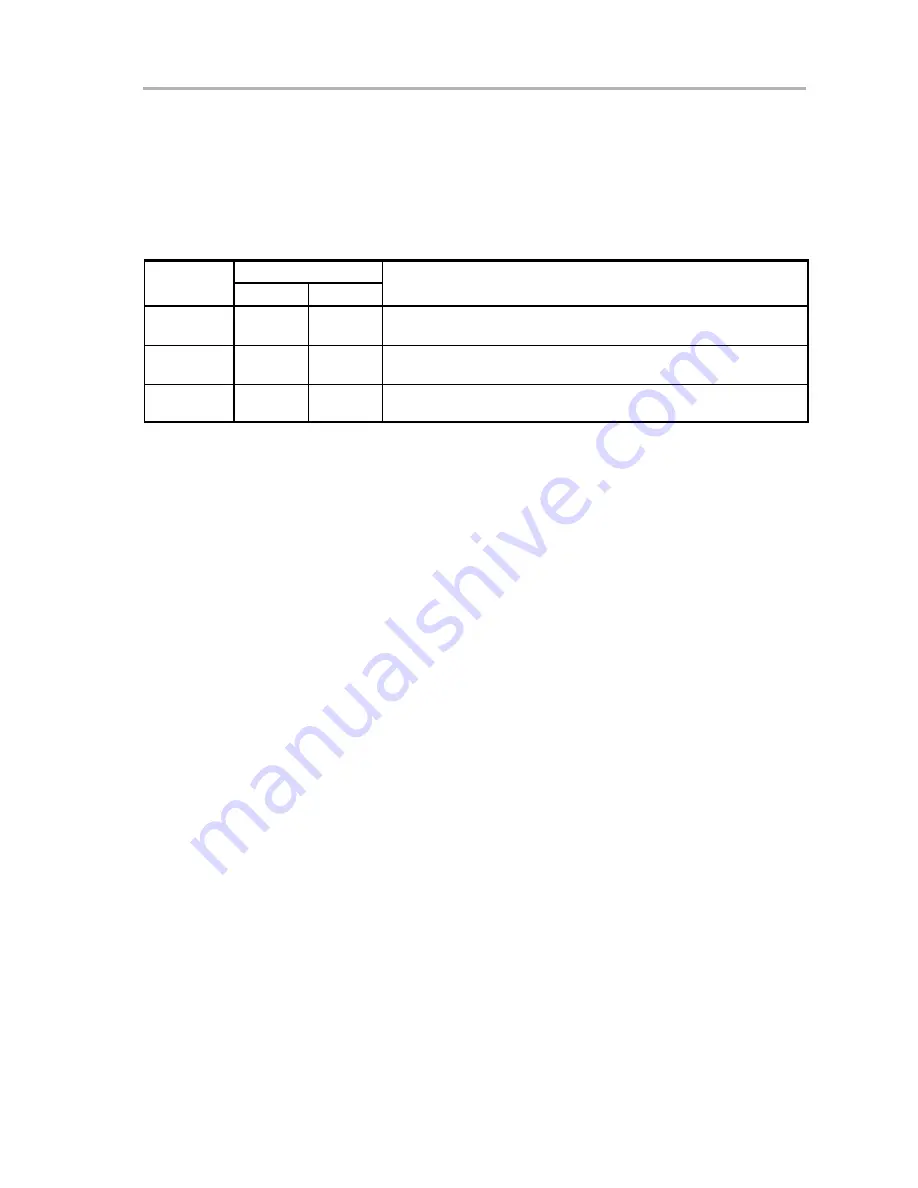

Table 3 - 5 shows the jumper setting configuration for a capacitive load drive.

Table 3 - 5. Capacitive Load Drive Output Jumper Settings

Jumper Setting

Reference

Unipolar

Bipolar

Function

W3

Close

Close

V

REF

H is disconnected from the inverting input of the output op-amp,

U2.

W5

2 - 3

1 - 2

Supplies power, V

SS

, to the negative rail of op-amp, U2, for bipolar

mode, or ties it to AGND for unipolar mode.

W15

Close

Open

Capacitive load drive output of DAC is routed to pin 1 of W15 jumper and

maybe used as the output terminal.

3.5

Optional Signal Conditioning Op-Amp (U8B)

One part of the dual package op-amp, OPA2132 (U8), is used for reference

buffering (U8A) while the other is unused. This unused op-amp (U8B) is left

for whatever op-amp circuit application the user desires to implement. The

1206 footprint for the resistors and capacitors surrounding the U8B op-amp

are not populated and made available for easy configuration. TP6 and TP7 test

points are not installed either so it is up to the user on how to connect the

±

input

signals to this op-amp. No test point has been made available for the output

due to space restriction, but a wire can be simply soldered to the output of the

op-amp via unused component pads that connects to it.

Once the op-amp circuit is realized the configuration becomes easy by simply

populating the corresponding components that matches the circuit designed

and leaving all other unused component footprints unpopulated.

Содержание DAC8574

Страница 1: ...DAC8574 Evaluation Module June 2003 Data Acquisition Digital Analog Converters User s Guide SLAU109 ...

Страница 17: ...PCB Layout 2 5 PCB Design and Performance Figure 2 7 Drill Drawing ...

Страница 19: ...EVM Performance 2 7 PCB Design and Performance Figure 2 9 INL and DNL Characterization Graph of DAC A ...

Страница 20: ...EVM Performance 2 8 Figure 2 10 INL and DNL Characterization Graph of DAC B ...

Страница 21: ...EVM Performance 2 9 PCB Design and Performance Figure 2 11 INL and DNL Characterization Graph of DAC C ...

Страница 22: ...EVM Performance 2 10 Figure 2 12 INL and DNL Characterization Graph of DAC D ...

Страница 24: ...2 12 ...