8 Application and Implementation

Note

Information in the following applications sections is not part of the TI component specification,

and TI does not warrant its accuracy or completeness. TI’s customers are responsible for

determining suitability of components for their purposes, as well as validating and testing their design

implementation to confirm system functionality.

8.1 Application Information

The DACx300x are single-channel and dual-channel buffered, force-sense output, voltage-output and current-

output smart DACs that include an NVM and internal reference, and available in a tiny 3-mm × 3-mm package.

• In voltage-output mode, short the OUTx and FBx pins for each channel. In current-output mode, leave the

FBx pins unconnected. The FBx pins function as inputs in comparator mode.

• The external reference must not exceed VDD, either during transient or steady-state conditions. For the best

Hi-Z output performance, use a pullup resistor on the VREF pin to VDD.

• In case VDD remains floating during the off condition, place a 100-kΩ resistor to AGND for proper detection

of the VDD off condition for voltage margining.

• All the digital outputs are open drain; use external pullup resistors on these pins.

• The interface protocol is detected at power-on, and the device locks to the protocol as long as VDD is on.

• When allocating nonoverlapping I

2

C addresses on a system I

2

C bus, consider the broadcast address as well.

I

2

C timeout can be enabled for robustness.

• SPI mode is 3-wire by default. Configure the GPIO pin as SDO in the NVM for SPI readback capability. The

SPI clock speed in readback mode is slower than in write mode.

• Power-down mode sets the DAC outputs to Hi-Z by default. Change the configuration appropriately for

different power-down settings. The DAC channels can also power-up with a programmed DAC code in NVM.

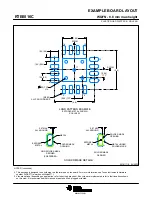

8.2 Typical Application

A power-supply margining and scaling circuit is used to trim, scale, or test the output of a power converter.

This example circuit is used to test a system by margining the power supplies for adaptive voltage scaling or to

program a desired value at the output. Adjustable power supplies, such as low-dropout regulators (LDOs) and

DC/DC converters, provide a feedback or adjust the input that is used to set the desired output. A precision

voltage-output DAC is the best choice for controlling the power-supply output linearly.

shows a control

circuit for a switch-mode power supply (SMPS) using the DACx300x. Typical applications of power-supply

margining are communications equipment, enterprise servers, test and measurement, and general-purpose

power-supply modules.

SMPS / LDO

R

1

R

2

V

FB

SENSE

PH

GND

V

OUT

IN

BOOT

C

L

C

B

L

VDD

V

IN

VOUT/

IOUT

VOUT/

IOUT

DAC

REG

DAC

BUF

DAC

REG

DAC

BUF

NVM

Internal

Reference

LDO

Output Configuration

Logic

VREF

CAP

AGND

Digital Inter

face

SCL/SYNC

SDA/SCLK

A0/SDI

PROTECT

R

3

R

3

1.5

μ

F

0.1

μ

10 k

Ω

Power-supply: 0

DACx300x

Power-supply: 1

Figure 8-1. Voltage Margining and Scaling

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

72

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: