Similar to I

2

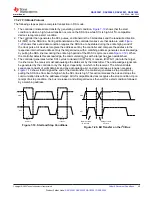

C, PMBus is a variable length packet of 8-bit data bytes, each with a receiver acknowledge,

wrapped between a start and stop bit. The first byte is always a 7-bit

target address

followed by a

write

bit,

sometimes called the

even address

, that identifies the intended receiver of the packet. The second byte is an

8-bit

command

byte, identifying the PMBus command being transmitted using the respective command code.

After the command byte, the transmitter either sends data associated with the command to write to the receiver

command register (from least significant byte to most significant byte; see also

), or sends a new start

bit indicating the desire to read the data associated with the command register from the receiver. Then the

receiver transmits the data following the same least significant byte first format; see also

Table 7-7. PMBus Update Sequence

MSB

....

LSB

ACK

MSB

...

LSB

ACK

MSB

...

LSB

ACK

MSB

...

LSB

ACK

Address (A) byte

Command byte

Data byte - LSDB

Data byte - MSDB

(Optional)

DB [31:24]

DB [23:16]

DB [15:8]

DB [7:0]

Table 7-8. PMBus Read Sequence

S

MSB

…

R/W

(0)

ACK

MSB

…

LSB

ACK

Sr MSB …

R/W

(1)

ACK

MSB

…

LSB

ACK

MSB

…

LSB

ACK

Address byte

Command byte

Sr

Address byte

LSDB

MSDB (Optional)

From controller

Target

From controller

Target

From controller

Target

From target

Controller

From target

Controller

The DACx300x I

2

C interface implements some of the PMBus commands.

commands that are implemented in DACx300x.The DAC uses DAC-X-MARGIN-LOW, DAC-X-MARGIN-HIGH

bits, SLEW-RATE-X, and CODE-STEP-X bits for PMBUS-OPERATION-CMD-X. To access multiple channels,

write the PMBus page address specified in

to the PMBUS-PAGE register first, followed by a write to

the channel-specific register.

Table 7-9. PMBus Operation Commands

REGISTER

PMBUS-OPERATION-CMD-X[15:8]

DESCRIPTION

PMBUS-OP-CMD-X

00h

Turn off

80h

Turn on

94h

Margin low

A4h

Margin high

The DACx300x also implement PMBus features such as group command protocol and communication timeout

failure. The CML bit in the PMBUS-CML register indicates a communication fault in the PMBus. This bit is reset

by writing 1.

To get the PMBus version, read the PMBUS-VERSION register.

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

40

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: