7.4.5.1.2 Programmable Slew-Rate Control

When the DAC data registers are written, the voltage on DAC output (V

OUT

) immediately transitions to the new

code following the slew rate and settling time specified in the

Electrical Characteristics

.

The slew rate control feature allows the user to control the rate at which the output voltage (V

OUT

) changes.

When this feature is enabled (using the SLEW-RATE-X[3:0] bits), the DAC output changes from the current

code to the code in the DAC-X-MARGIN-HIGH or DAC-X-MARGIN-LOW registers (when margin high or low

commands are issued to the DAC) using the step size and time-period per step set in CODE-STEP-X and

SLEW-RATE-X bits in the DAC-X-FUNC-CONFIG register:

• SLEW-RATE-X defines the time-period per step at which the digital slew updates.

• CODE-STEP-X defines the number of LSBs by which the output value changes at each update, for the

corresponding channels.

and

show different settings available for CODE-STEP-X and SLEW-RATE-X. With the

default slew rate control setting of no-slew, the output changes immediately at a rate limited by the output drive

circuitry and the attached load.

When the slew rate control feature is used, the output changes happen at the programmed slew rate.

shows that this configuration results in a staircase formation at the output. Do not write to CODE-STEP-X,

SLEW-RATE-X, or DAC-X-DATA during the output slew operation.

calculating the slew time (t

SLEW

).

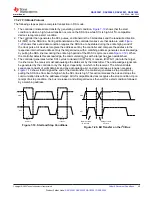

MARGIN-LOW

MARGIN-HIGH

TIME PERIOD

CODE-STEP

t

SLEW

Figure 7-10. Programmable Slew-Rate Control

t

SLEW

=

SLEW_RATE × MARGIN_HIGH − MARG 1

CODE_STEP

(6)

where:

• SLEW_RATE is the SLEW-RATE-X setting specified in

• CODE_STEP is the CODE-STEP-X setting specified in

.

• MARGIN_HIGH is the DAC-X-MAGIN-HIGH specified in

• MARGIN_LOW is the DAC-X-MAGIN-LOW specified in

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

Copyright © 2022 Texas Instruments Incorporated

37

Product Folder Links: