HPR

HPL

AGND

Application Information

www.ti.com

15

Application Information

15.1 Minimizing Click and Pop

To minimize the audible click and pop heard through a headphone, maximize the input signal through the

corresponding volume (gain) control registers and adjust the output amplifier gain accordingly to achieve

the your desired signal gain. For example, setting the output of the headphone amplifier to -24dB and

setting the input volume control gain to 24dB will reduce the output offset from 7mV (typical) to 2.2mV

(typical). This will reduce the audible click and pop noise significantly while maintaining a 0dB signal gain.

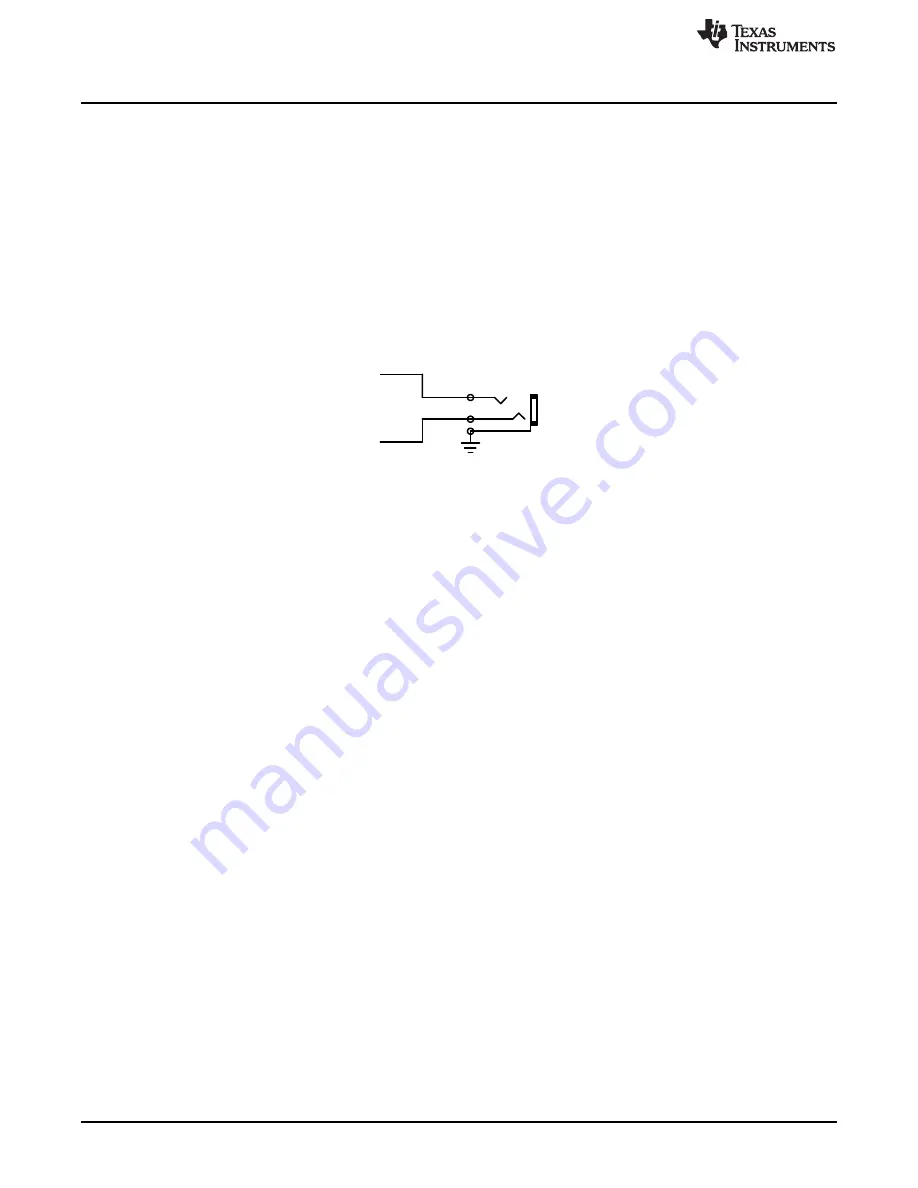

15.2 Signal Ground Noise

The LM49100 has proprietary suppression circuitry, which provides an additional -50dB (typical)

attenuation of the headphone ground noise and its incursion into the headphone. For optimum utilization

of this feature, the headphone jack ground should connect to the AGND (E3) bump.

Figure 18. Suppression Circuitry

15.3 I

2

C Pin Description

SDA: This is the serial data input pin.

SCL: This is the clock input pin.

ADDR: This is the address select input pin.

15.4 I

2

C Compatible Interface

The LM49100 uses a serial bus which conforms to the I

2

C protocol to control the chip's functions with two

wires: clock (SCL) and data (SDA). The clock line is uni-directional. The data line is bi-directional (open-

collector). The LM49100's I

2

C compatible interface supports standard (100kHz) and fast (400kHz) I

2

C

modes. In this discussion, the master is the controlling microcontroller and the slave is the LM49100.

The I

2

C address for the LM49100 is determined using the ADDR pin. The LM49100's two possible I

2

C chip

addresses are of the form 111110X

1

0 (binary), where X

1

= 0, if ADDR pin is logic LOW; and X

1

= 1, if

ADDR pin is logic HIGH. If the I

2

C interface is used to address a number of chips in a system, the

LM49100's chip address can be changed to avoid any possible address conflicts.

The bus format for the I

2

C interface is shown in

Figure 19

and the timing diagram is shown in

Figure 20

.

The bus format diagram is broken up into six major sections:

•

The "start" signal is generated by lowering the data signal while the clock signal is HIGH. The start

signal will alert all devices attached to the I

2

C bus to check the incoming address against their own

address.

•

The 8-bit chip address is sent next, most significant bit first. The data is latched in on the rising edge of

the clock. Each address bit must be stable while the clock level is HIGH.

•

After the last bit of the address bit is sent, the master releases the data line HIGH (through a pull-up

resistor). Then the master sends an acknowledge clock pulse. If the LM49100 has received the

address correctly, then it holds the data line LOW during the clock pulse. If the data line is not held

LOW during the acknowledge clock pulse, then the master should abort the rest of the data transfer to

the LM49100.

•

The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock

level is stable HIGH.

14

AN-1622 LM49100 Evaluation Board»

SNAA043A – October 2007 – Revised May 2013

Submit Documentation Feedback

Copyright © 2007–2013, Texas Instruments Incorporated