A-Cute

User Manual

16

September 12, 2016

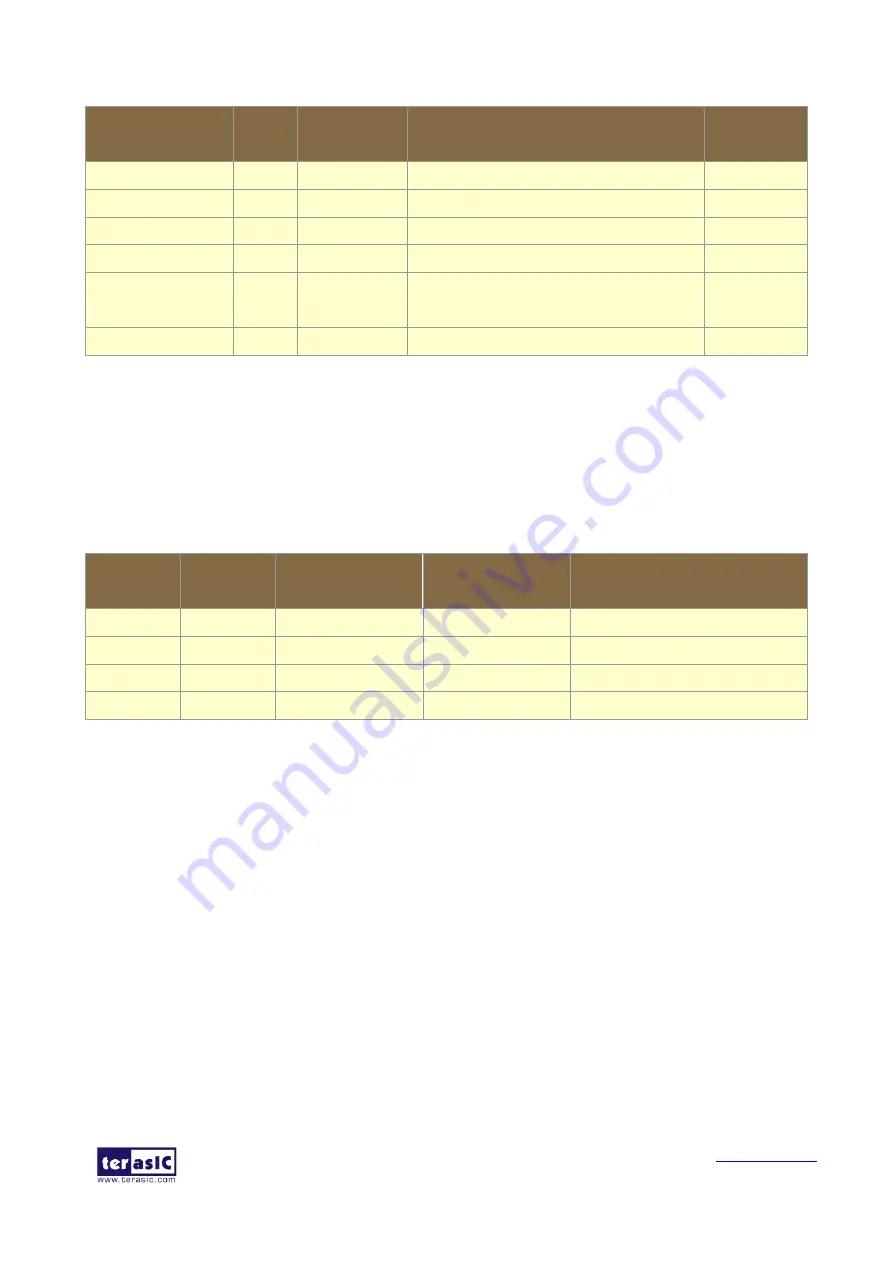

Table 3-2 Pin assignment of Motor Driver interface

SCD Signal Name

GPIO

Pin No.

FPGA Pin No.

on GPIO 0

Description

I/O Standard

MTRR_N

5

PIN_A2

Right Motor Negative signal.

OUT, 3.3V

MTRR_P

6

PIN_A3

Right Motor Positive signal.

OUT, 3.3V

MTRL_P

7

PIN_B3

Left Motor Positive signal.

OUT, 3.3V

MTRL_N

8

PIN_B4

Left Motor Negative signal.

OUT, 3.3V

MTR_Sleep_n

9

PIN_A4

Logic high to enable device

logic low to enter low-power sleep mode

OUT, 3.3V

MTR_Fault_n

10

PIN_B5

Pulled logic low with fault condition

IN, 3.3V

The device integrates two H-bridges that use NMOS low-side drivers and PMOS high-side drivers

and current sensor regulation circuitry. The DRV8848 can be powered with a supply range between

4 to 18 V and is capable of providing an output current to 1-A rms.

shows the logic for the inputs of H-Bridge control.

Table 3-3 H-Bridge Control Signal

MTRR_P

MTRL_P

MTRR_N

MTRL_N

MTRR_OUT_Ap

MTRL_OUT_Bp

MTRR_OUT_An

MTRL_OUT_Bn

Function (DC Motor)

0

0

Z

Z

Coast (fast decay)

0

1

L

H

Reverse

1

0

H

L

Forward

1

1

L

L

Brake (slow decay)