UM1519

STM3220G-EVAL demonstration board

Doc ID 022813 Rev 2

13/40

Note:

A test point (TP2) is available on the board for the PTP_PPS feature test.

The Ethernet PHYU5 can be powered down by regulating PB14.

1.9 SRAM

The 16 Mbit SRAM is connected to the FSMC bus of the STM32F207IGH6 which shares the

same I/Os with CAN1 bus. JP3 and JP10 must not be fitted for SRAM and LCD application.

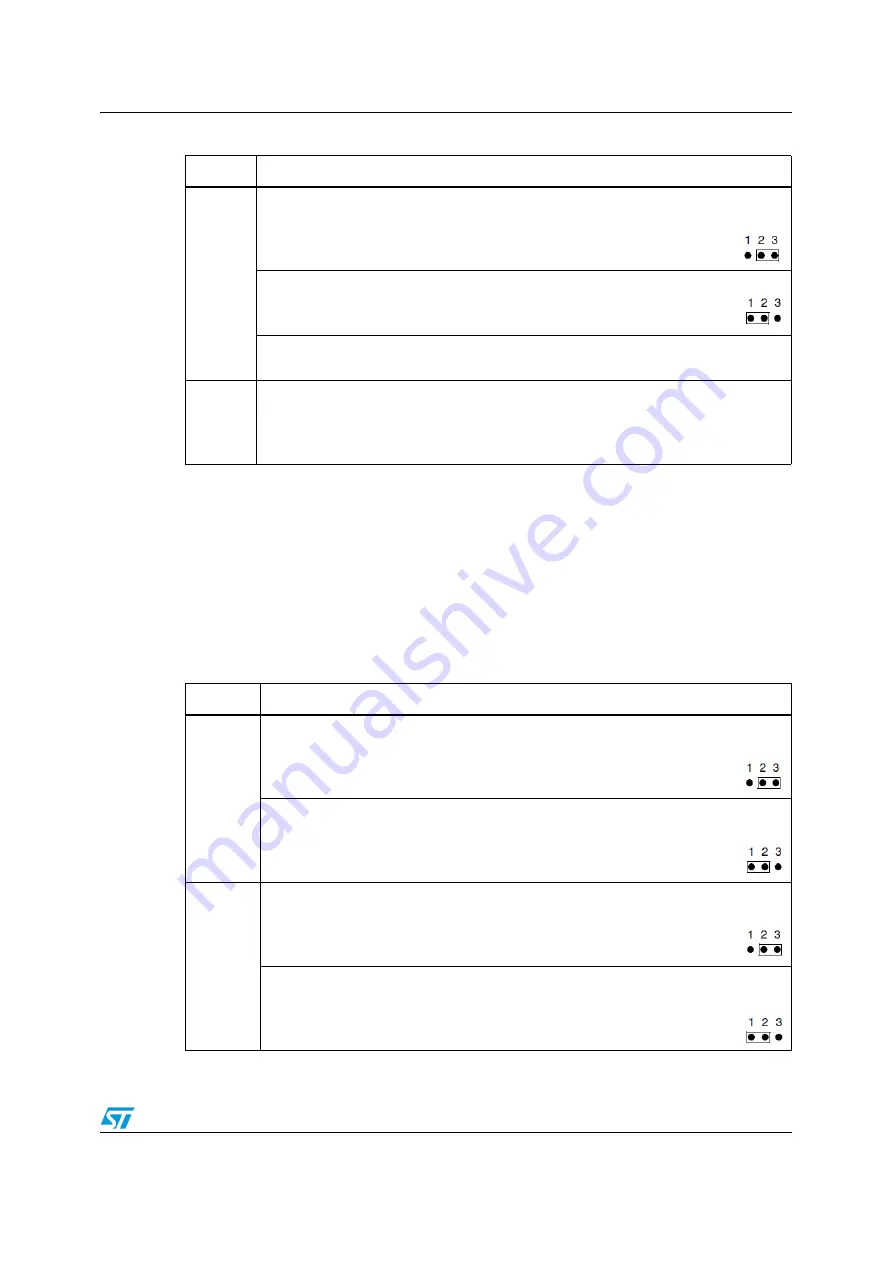

JP5

To provide 25 MHz clock for MII or 50 MHz clock for RMII by

MCO at PA8, set JP5 as shown (default setting):

To provide 25 MHz clock by external crystal X1 (for MII interface

mode only) set JP5 as shown:

When clock is provided by external oscillator U3, JP5 must not be fitted

(default setting).

SB1

SB1 is used to select clock source only for RMII mode.

To connect the clock from MCO to RMII_REF_CLK, close SB1.

The resistor R212 must be removed in this case.

Default setting: open

Table 4.

Ethernet related jumpers and solder bridges (continued)

Jumper

Description

Table 5.

SRAM related jumpers

Jumper

Description

JP1

Connect PE4 to SRAM as A20 by setting JP1 as shown (default

setting):

Connect PE4 to trace connector CN13 as TRACE_D1 by setting

JP1 as shown:

JP2

Connect PE3 to SRAM as A19 by setting JP2 as shown (default

setting):

Connect PE3 to trace connector CN13 as TRACE_D0 by setting

JP2 as shown: