41

Functions of the XCL-V500

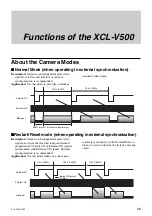

XCL-X700/V500

■

Trigger Pulse Specifications

DC IN connector

DIGITAL IF connector

Input signals meeting the input specifications above converted to the signal level of the LVDS system (output

by the 3.3 V IC). Be aware that if the signals fail to meet the following conditions, the camera module will not

recognize the input signals properly.

H level: 1.5 V to 1.7 V

L level: 0.8 V to 1.0 V

■

WEN Output Specifications (only for the DC IN connector)

Outputs WEN signals synchronized with the falling edge of Internal-VD, corresponding to the start of video signal

output in Trigger Mode1/2.

■

LVAL/FVAL Output

Specifications (only for the

DIGITAL IF connector)

Outputs Camera Link-compatible signals.

H level: approx. 1.5 V

L level: approx. 1.0 V

(When terminated with the specified register)

The following signals are output as enable signals.

DVAL: High (fixed)

LVAL: Horizontal blanking signals (HBLKG)

FVAL: Vertical blanking signals (VBLKG)

Outputs VAL signals for FVAL while using the High-

rate scan II function.

VAL: While using High-rate scan II

Effective image interval: High

BLKG interval: Low

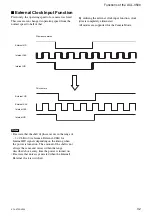

■

External-CLK Specifications

(common to the DC IN

/DIGITAL IF connectors)

Supports LVDS input signals for both types of

connectors.

Specifications for the External-CLK input are as follows.

CLK-Duty: 50%

The range of input clock signal frequency: 29.5 to 59

MHz

Input signals meeting the input specifications above

converted to the signal level of the LVDS system

(output by the 3.3 V IC). Be aware that if the signals

fail to meet the following conditions, the camera

module will not recognize the input signals properly.

H level: 1.5 V to 1.7 V

L level: 0.8 V to 1.0 V

Notes

• Input the external input signals after the power is

turned on. If you input external input signals before

the power is turned on, this may result in a

malfunction of the camera module.

This applies for External-clock/HD/VD and the

trigger pulse.

• When using external clock signals, be sure to input

continuous external clock signals, and then enter the

EXTHVCLK (External HD/VD/CLK signal input

Selection) command that specifies an input path for

external clock signals before entering the CLKSEL

(Master Clock Selection) command. Select an input

path for external clock signals first, and then enter the

CLKSEL (Master Clock Selection) command. When

changing an input path for external clock signals as

well, change the clock setting from external clock to

normal internal clock signals first, and then change

the clock setting again to external clock signals

observing the condition above. Be aware that if this

condition is not observed, the camera module may

stop the operation.

When changing the clock setting from external clock

to normal internal clock signals, stop inputting

external clock signals after the clock mode has

changed to the internal clock mode completely. Be

sure to start the operation by external clock signals

observing the condition above. Be aware that if this

condition is not observed, the camera module may

stop the operation.

• When using external clock synchronization, input

External-HD signals with a 780 count interval

derived from an external clock with frequency

division for the external-HD signals. Be aware that if

this condition is not observed, both horizontal sync

signals and video output signals stop.

2.0

µ

s~1/4 s

0~0.6 V

2~5 V

The voltage measured when the input impedance is 10 k

Ω

or

more

0 V

The voltage measured when terminated with 10 k

Ω

or more

5 V