RDR-GXD310/HXD710/HXD910

3-11

3-12

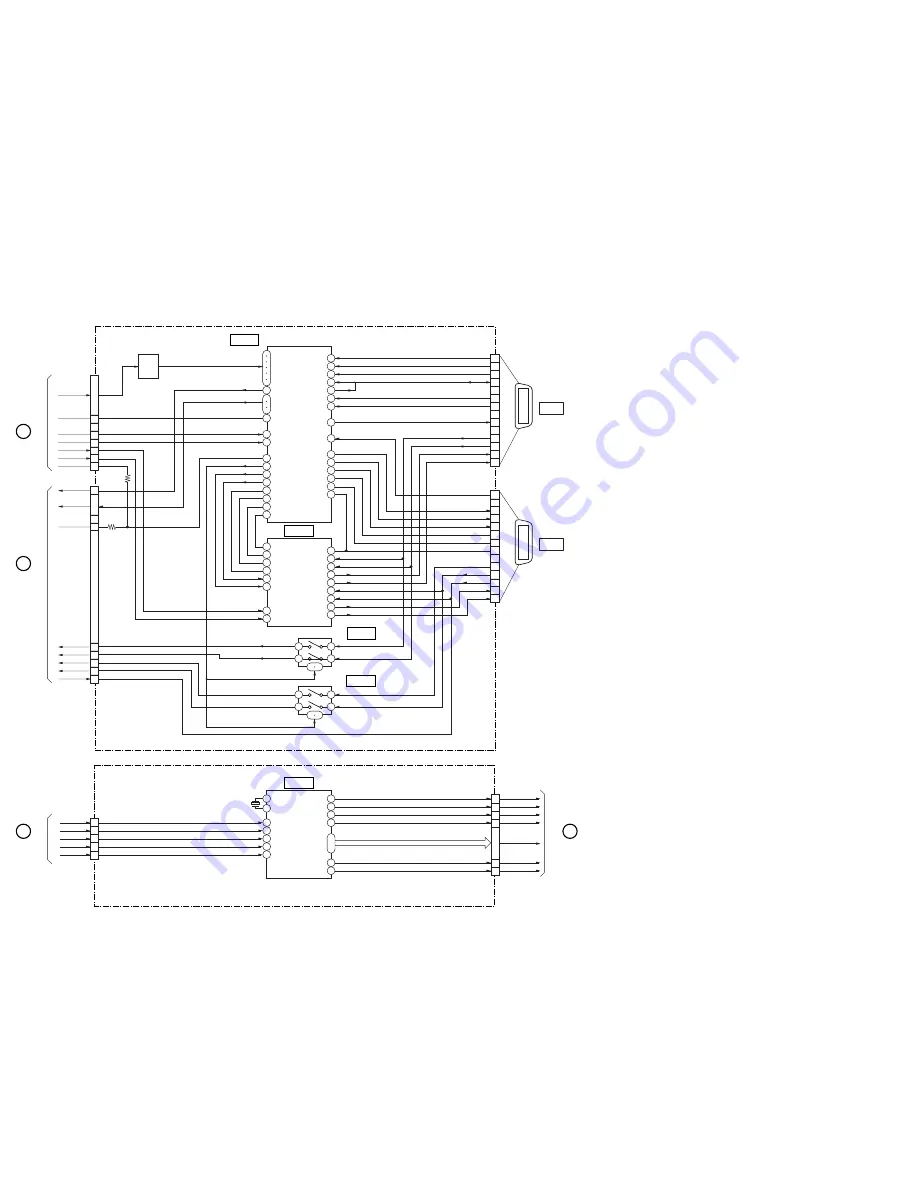

3-6. ER-036, DE-001 BOARD BLOCK DIAGRAM

IC105

IC106

IC104

IC103

TO

AV-096 BOARD

CN901

TO

AV-096 BOARD

CN902

ER-036 BOARD

9

TO

AV-096 BOARD

CN3001

4

TO

A-004 BOARD

CN462

5

8

DE-001 BOARD

IC001

20

15

11

7

16

8

19

6

2

3

1

V IN

R IN

G IN

BI/CQ

BLAKING IN

LINE 3/

DECODER

CN103

LINE 1 - TV

CN104

FUNCTION SW IN

V/Y OUT

A(L)IN

A(R)IN

A(L)OUT

A(R)OUT

20

19

11

15

7

16

10

8

6

2

3

1

13

17

19

21

23

R/C

G

B

ALL MUTE

CVBS/Y OUT

FS2

FB

C OUT

AUXB

AUXG

AUX R/C

AUX CVBS/Y

LI CVBS

CVBS/Y OUT

R/C OUT

G OUT

B OUT

LI FB OUT

FS1

FS LI OUT

AUX L IN

AUX R IN

AUX L OUT

AUX R OUT

LI L IN

LI R IN

LI L OUT

LI R OUT

SCL

SDA

FSW

PARALLEL1

FS AUX

FSL1

ASW4

ASW3

ASW2

ASW1

ASW1

ASW2

ASW3

ASW4

FS L1IN

FS AUX IN

DA R IN

DA L IN

27

25

6

4

2

24

11

9

5

7

28

V IN

V/Y OUT

R/C OUT

G OUT

BO/CI

BLAKING OUT

FUNCTION SW OUT

AVLINK

BUFFER

A(L)IN

A(R)IN

A(L)OUT

A(R)OUT

27

50

28

29

30

32

24

36

31

51

34

44

42

40

38

5

15

17

21

23

3

7

52

47

46

41

14

10

8

6

4

2

48

22

20

18

22

20

21

23

14

16

15

17

24

12

14

2

9 10

15

8

9

12

10

7

6

2

1

12

14

2

9 10

15

Q104-109

L3B

L3G

L3RC

XVMUTE

SCL

SDA

EUAUOUTR

EUAUOUTL

VY AD

EUAUINL3

EUAUINR3

EUAUINL1

EUAUINR1

AVLINK

ERC

ERV

ERY

ERB

ERR

ERG

FSW

EURO MUTE

CN105

CN106

20

10

18

16

12

22

63

FE_DATA0-7

FE_RESET

CN002

FE_CLK

FE_VALID

FE_PACKETSYNC

DTT_SCL1

DTT_SDA1

FE_RESET

FE_CLK

FE_VALID

FE_PSYNC

FE_DATA0-7

DTT_SCL1

DTT_SDA1

62

7

6

5

4

18

14

17

16

2

1

58

59

57

54

53

26

25

11

|

18

4

|

7

9

|

12

3

4

6

8

9

20.48MHz

X001

IF1

CN001

IF2

IFAGC

SCL

SDA

IF1

IF2

IFAGC

SCL

SDA

Содержание RDR-GXD310

Страница 6: ...MEMO 6 ...

Страница 36: ...1 30E MEMO ...

Страница 103: ...MEMO 5 10E ...

Страница 109: ...6 6E MEMO ...