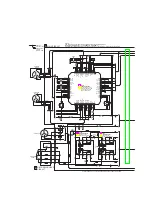

SECTION 6

DIAGRAMS

6-1. BLOCK DIAGRAMS

— BD SECTION —

— 37 —

— 38 —

MDS-JA50ES

OPTICAL PICK-UP BLOCK

(KMS-210A/J-N)

IV-AMP

IV-AMP

J

C B

D A

F

E

6

2

3

6

5

VC

7

1

IC172

BUFFER

48

47

J

I

RF AMP

46 45 44 43

RF AGC

& EQ

BPF

2

3

4

5

6

7

IV AMP

IV AMP

6

8

VC

RV101

E-F

BALANCE

9

1

+2.5V

GENERATOR

VC

16

12

D101

TEMP

AMP

TEMPR

+5V

TEMPI

10

11

Q101

APC

APCREF

LASER ON

SWITCH

LASER

POWER

RV102

PD

14 15

42

TRACKING

ERROR

AMP

AUX

SW

PEAK &

BOTTOM

ABCD

AMP

FOCUS

ERROR

AMP

AT

AMP

30

26

29

27

25

23

22

41

34

38

39

37

35

31

33

SERIAL

PARALLEL

DECODER

17 18 19 20

4

RF AMP

IC101

+5V

HR901

OVER

WRITE

HEAD

4

2

IC122

Q162,163

APC

HIGH

POWER

LD

Q164

HF

MODULE

SWITCH

SLED/SPINDLE MOTOR DRIVE,

FOCUS/TRACKING COIL DRIVE

IC151

HEAD

DRIVE

Q181,182

11

14

15

17

18

OVER WRITE

HEAD DRIVE

IC181

1

19

2

3

9

5

IC102

4

2

VC

DRIVER

DRIVER

DRIVER

L.F

MOD

H.F

MOD

26

29

TRK+

TRK–

11

8

15

13

TRACKING

COIL

FOCUS

COIL

2

2

M

M101

SLED

MOTOR

22

24

M

M102

SPINDLE

MOTOR

2

2

CLOCK

DETECTOR

3

Q151

RESET

SWITCH

33

DRIVER

20

19

18

17

6

5

31

32

TFDR

TRDR

FRDR

FFDR

SFDR

SRDR

SPFD

SPRD

FS4

DIGITAL SIGNAL PROCESSOR,

DIGITAL SERVO SIGNAL PROCESSOR,

EFM/ACIRC ENCODER/DECODER

IC121

SUBCODE

PROCESSOR,

READER/

GENERATOR

14

EFM

MOD/DEMOD

45

58

DIN

PLL

REGISTER

FILTER

PLL

4

EFM

TIMING

GENERATOR

DIGITAL

CLV

PROCESSOR

TIMING

GENERATOR

&

CLOCK

GENERATOR

AUDIO

DATA

CONTROL

ECC

ENCODER

DECODER

32K RAM

30

29

27

28

DIGITAL

AUDIO

IN/OUT

20

21

15

FILTER

31

94

93

82

ADIP

DEMOD

ADIP

DECODER

ANALOG

MUX

68

65

64

66

67

77

76

69

VC

5

A/D

CONV

8

9

10

16

CPU

IF

24

11

4

SERVO

CONTROL

DIRC

7

SERVO

AUTO

SEQUENCER

PROCESSOR

APC

PWM

GEN

5

SERVO DSP/PWM GENERATOR

FOCUS/TRACKING/

SLED SERVO & PWM

6

4

3

2

98

99

DFCT

FOK

SHCK

OFTRK

COUT

6

84

LD

32

33

90

35

BCK

LRCK

FS4

XTAI

SENS

CONTROL

12

85 86 87 89 91 92

6

51 52 49 53

DICV

DIFI

DIPD

DIFO

SQSY

DQSY

DIN

DOUT

DIDT

DODT

DTO

DTI

C2PO

TRDR

TFDR

FFDR

FRDR

SRDR

SFDR

SENS

SWDT

SCLK

XLAT

XRST

REC

SRDT

AUX

BOTM

PEAK

ABCD

FE

TE

SE

VC

SPFD

SPRD

60

62

61

63

CLTV

FILI

PCO

FILO

EFMO

RFI

RF

AUX

BOTM

PEAK

ABCD

FE

ADFM

ADIN

TE

SE

TLB

ADFG

XRST

SWDT

SCLK

XLAT

PD

VC

A

B

C

D

E

F

FI

FO

FCS+

FCS–

SLED–

SLED+

SPDL+

SPDL–

4

2

IC182

8

LDDR

AAPC

DAPC

I

WRPWR

LIMIT

INSW

OUTSW

HDS

HUS

PROTECT

REFLECT

5

-1

-2

S102-1

PROTECT

S102-2

REFLECT

S101

LIMIT IN

SW191

LOAD IN DET

SW192

LOAD OUT DET

SW193

HEAD DOWN

DET

SW194

HEAD UP DET

IC171

MEMORY

6

5

SDA

SCL

SDA

SCL

WRPWR

FG

SHCK

FOK

DFCK

512FS

SQSY

SCTX

SWDT

SCLK

XLAT

SRDT

SENS

LRCK

BCK

C2PO

L OUT

L IN

HU

HD

DATA

DODT

DOUT

LDON

MOD

REC

DIGITAL

SECTION

(Page 39)

A

09

Signal path

:PB

:REC

:PB (Digital out)

:REC (Digital in)

P-P

TFIL

THID

TENV

M

M

M191

LOADING MOTOR

M192

HEAD MOTOR

XRST

Содержание MDS-JA50ES / Mode d’emploi

Страница 8: ... 8 This section is extracted from instruction manual ...

Страница 9: ... 9 ...

Страница 10: ... 10 ...

Страница 11: ... 11 ...

Страница 12: ... 12 ...

Страница 13: ... 13 ...

Страница 14: ... 14 ...

Страница 15: ... 15 ...

Страница 16: ... 16 ...

Страница 17: ... 17 ...

Страница 18: ... 18 ...

Страница 19: ... 19 ...

Страница 20: ... 20 ...

Страница 21: ... 21 ...

Страница 22: ... 22 ...

Страница 23: ... 23 ...

Страница 24: ... 24 ...

Страница 25: ... 25 ...

Страница 41: ......

Страница 42: ......

Страница 43: ......

Страница 44: ......

Страница 45: ......

Страница 46: ......

Страница 47: ......

Страница 48: ......

Страница 49: ......

Страница 50: ......

Страница 51: ......

Страница 52: ......

Страница 53: ......

Страница 54: ......

Страница 55: ......

Страница 56: ......