— 99 —

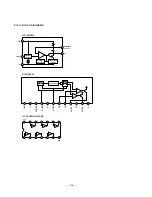

• IC409 Sampling Rate Converter (CXD8517Q)

Data input

Input data fs word clock input (Schemidt)

Input data bit clock input

Input data format setting input 0 (Fixed at “L”)

Input data format setting input 1 (Fixed at “L”)

+5V power supply

Input data fs reference clock input (512fs, 384fs, 256fs, 128fs)

Output data format setting input 0 (Fixed at “L”)

Output data format setting input 1 (Fixed at “L”)

Initializing input (Schmidt). “L”: Initializing, “H”: Normal operation

Not used

Ground

Inverter input for oscillating the crystal oscillator (512fo master clock input)

Inverter output for oscillating the crystal oscillator (Not used)

+5V power supply

Oscillation clock division output: 256fs (Not used)

Ground

Input data through output mode setting input. “L”: Normal operation, “H”: Through

(When through: Effective operation output only for deemphasis, attenuation) (Fixed at “L”)

FI128 clock input division ratio setting input (Fixed at “L”)

FI128 clock input division ratio setting input (Fixed at “L”)

Test input 0 (Not used)

Not used

Test input 1 (Fixed at “L”)

Test input 2 (Fixed at “L”)

Test input 3 (Fixed at “L”)

fs conversion ratio measurement condition monitor output (Not used)

+5V power supply

Not used

Data output (fso output)

Output data bit clock input/output

Output data fs word clock input/output

Not used

Data output mute setting input. “L”: Mute, “H”: Normal operation

Synchronized with LRCK (“0" data only for DATAO output) (Fixed at “H”)

Deemphasis setting input. “L”: OFF, “H”: ON (Fixed at “L”)

Deemphasis setting output fso frequency selection input 1 (Fixed at “L”)

Deemphasis setting output fso frequency selection input 2 (Fixed at “L”)

Ground

Attenuation, mode setting data latch pulse input

Attenuation, mode setting clock input

Attenuation, mode setting data input

Sync mode selection. “L”: Slave, “H”: Master (Fixed at “L”)

Not used

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

DATAI

LRCKI

BCKI

MI0

MI1

VDD

FI128

MO0

MO1

INIT

NC

GND

XI

XO

VDD

XO2

GND

PASS

FIS0

FIS1

TEST

NC

NC

TEST1

TEST2

TEST3

STA

VDD

NC

DATAO

BCKO

LRCKO

NC

NC

MUTE

DEMP

FS1

FS2

GND

XLAT

SCK

SWDT

SLAVE

NC

I

I

I

I

I

—

I

I

I

I

—

—

I

O

—

O

—

I

I

I

O

—

—

I

I

I

O

—

—

O

I/O

I/O

—

—

I

I

I

I

—

I

I

I

I

—

Function

I/O

Pin No.

Pin Name

Содержание MDS-B5

Страница 2: ... 2 ...

Страница 5: ... 5 SECTION 1 GENERAL This section is extracted from instruction manual ...

Страница 6: ... 6 ...

Страница 7: ... 7 ...

Страница 8: ... 8 ...

Страница 9: ... 9 ...

Страница 10: ... 10 ...

Страница 11: ... 11 ...

Страница 12: ... 12 ...

Страница 13: ... 13 ...

Страница 14: ... 14 ...

Страница 15: ... 15 ...

Страница 16: ... 16 ...

Страница 17: ... 17 ...

Страница 18: ... 18 ...

Страница 19: ... 19 ...

Страница 20: ... 20 ...

Страница 21: ... 21 ...

Страница 22: ... 22 ...

Страница 23: ... 23 ...

Страница 24: ... 24 ...

Страница 25: ... 25 ...

Страница 26: ... 26 ...

Страница 27: ... 27 ...

Страница 28: ... 28 ...

Страница 29: ... 29 ...

Страница 30: ... 30 ...

Страница 31: ... 31 ...

Страница 32: ... 32 ...

Страница 49: ......

Страница 50: ......

Страница 51: ......

Страница 52: ......

Страница 53: ......

Страница 54: ......

Страница 55: ......

Страница 56: ......

Страница 57: ......

Страница 58: ......