— 90 —

— 89 —

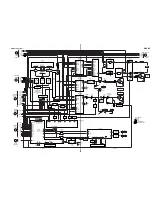

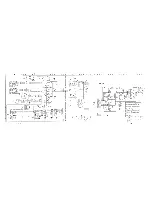

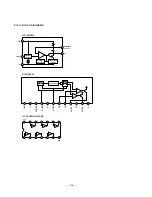

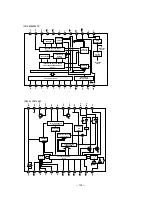

5-13. IC PIN FUNCTIONS

• IC101 RF Amplifier (CXA1981AR)

Pin No.

Pin Name

I/O

Function

Middle point voltage (2.5V) generation output

Input of signal from optical block detector

F operation amplifier input

F operation amplifier output

Front monitor. Connected to photo diode

Input pin for setting laser power

Temperature sensor connection input

Ground

APC LD amplifier output

Not used

Temperature sensor reference voltage output

Input of reset signal from Q403. Reset: “L”

Input of write data signal from system controller (IC301)

Input of clock signal from system controller (IC301)

Input of latch signal from system controller (IC301)

Reference voltage output (Not used)

Not used

Not used (Connected to VC)

Power supply (+5V)

Not used

Output of tracking error signal to CXD2535CR (IC121)

Input of add signal to tracking error

Sled error LPF input

Output of sled error signal to CXD2535CR (IC121)

ADIP FM signal output

Inputs ADIP FM signal by AC coupling

Connection of external capacitor for ADIP AGC

Output of ADIP dual FM signal to CXD2535CR (IC121) (22.05 kHz±1 kHz)

Output of auxiliary signal to CXD2535CR (IC121)

Output of focus error signal to CXD2535CR (IC121)

Not used

Output of light amount signal to CXD2535CR (IC121)

Output of bottom hold signal of light amount signal to CXD2535CR (IC121)

Output of peak hold signal of light amount signal to CXD2535CR (IC121)

Connection of RF AGC circuit external capacitor

Output of playback EFM RF signal to CXD2535CR (IC121)

Internal circuit constant setting input. 22 kHz BPF center frequency

Inputs RF signal by AC coupling

Output of RF signal

Inputs MO RF signal by AC coupling

Output of MO RF signal

Input of signal from optical block detector

O

I

I

O

I

I

I

–

O

O

O

I

I

I

I

O

O

I

–

I

O

I

I

O

O

I

I

O

O

O

I

O

O

O

I

O

I

I

O

I

O

I

VC

A to F

FI

FO

PD

APCREF

TEMPI

GND

AAPC

DAPC

TEMPR

XRST

SWDT

SCLK

XLAT

VREF

TENV

THLD

VCC

TFIL

TE

TLB

CSLED

SE

ADFM

ADIN

ADAGC

ADFG

AUX

FE

FLB

ABCD

BOTM

PEAK

RFAGC

RF

ISET

AGCT

RFO

MORFI

MORFO

I, J

1

2 to 7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47, 48

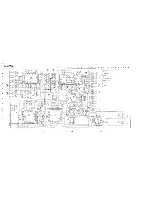

• IC121 Digital signal procesor, digital servo processor, EFM/ACIRC encoder/decoder (CXD2535CR)

FS256

FOK

DFCT

SHCK

SHCKEN

WRPWR

DIRC

SWDT

SCLK

XLAT

SRDT

SENS

ADSY

SQSY

DQSY

XRST

TEST4

CLVSCK

TEST5

DOUT

DIN

FMCK

ADER

REC

DVSS

DOVF

DODT

DIDT

DTI

DTO

C2PO

BCK

LRCK

XTAO

XTAI

MCLK

XBCK

DVDD

WDCK

RFCK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

O

O

O

O

I

I

I

I

I

I

O

O(3)

O

O

O

I

I

O

I

O

I

O

O

I

–

I

I

O

I

O(3)

O

O

O

O

I

O

O

–

O

O

Function

Pin No.

Pin Name

I/O

11.2896 MHz clock output (MCLK) (Not used)

Output of FOK signal to system controller (IC301)

Outputs “H” when focus is set

Outputs defect ON/OFF switching signal (Not used)

Outputs track jump detection signal to system controller (IC301)

Track jump detection enable input (Fixed at “H”)

Inputs laser power switching signal from system controller (IC301)

Not used (Fixed at “H”)

Inputs write data signal from system controller (IC301)

Inputs serial clock signal from system controller (IC301)

Inputs serial latch signal from system controller (IC301)

Outputs write data signal to system controller (IC301)

Outputs internal status (SENSE) to system controller (IC301)

ADIP sync signal output (Not used)

Output subcode Q sync (SCOR) to system controller (IC301)

Outputs “L” every 13.3 msec. Outputs “H” at all most mostly

Outputs digital-in U-bit CD format subcode Q sync (SCOR) to system controller (IC301).

Outputs “L” every 13.3 msec Outputs “H” at all most mostly

Inputs reset signal from Q403. Reset: “L”

Test input (Fixed at “L”)

Not used

Test input (Fixed at “L”)

Digital audio signal output

Digital audio signal input

ADIP FM demodulation clock signal output

ADIP CRC flag output. “H”:Error

Input of recording/playback switching signal from system controller (IC301)

Recording: “H”. Playback: “L”

Ground (Digital)

Digital audio output validity flag input (Fixed at “L”)

Input of data for digital audio output from CXD8633Q (IC901)

Output of data for digital audio input

Input of recording audio data signal from CXD2536CR (IC401)

Output of playback audio data signal to CXD2536CR (IC401)

Outputs C2PO signal to CXD2536CR (IC401) (Output indicating data error status)

Playback: C2PO (“H”). Digital recording: D.In-Vflag. Analog recording: “L”

Outputs bit clock signal (2.8224 MHz) to CXD2536CR (IC401) (MCLK)

Outputs L/R clock signal (44.1 kHz) to CXD2536CR (IC401) (MCLK)

For crystal

Input of system clock (512fs) for crystal

MCLK clock (22.5792 MHz) signal output (Not used)

Pin 32 (BCK) inversion output (Not used)

Power supply (+5V) (Digital)

WDCK clock (88.2 kHz) signal output (MCL) (Not used)

RFCK clock (7.35 kHz) signal output (MCLK) (Not used)

Содержание MDS-B5

Страница 2: ... 2 ...

Страница 5: ... 5 SECTION 1 GENERAL This section is extracted from instruction manual ...

Страница 6: ... 6 ...

Страница 7: ... 7 ...

Страница 8: ... 8 ...

Страница 9: ... 9 ...

Страница 10: ... 10 ...

Страница 11: ... 11 ...

Страница 12: ... 12 ...

Страница 13: ... 13 ...

Страница 14: ... 14 ...

Страница 15: ... 15 ...

Страница 16: ... 16 ...

Страница 17: ... 17 ...

Страница 18: ... 18 ...

Страница 19: ... 19 ...

Страница 20: ... 20 ...

Страница 21: ... 21 ...

Страница 22: ... 22 ...

Страница 23: ... 23 ...

Страница 24: ... 24 ...

Страница 25: ... 25 ...

Страница 26: ... 26 ...

Страница 27: ... 27 ...

Страница 28: ... 28 ...

Страница 29: ... 29 ...

Страница 30: ... 30 ...

Страница 31: ... 31 ...

Страница 32: ... 32 ...

Страница 49: ......

Страница 50: ......

Страница 51: ......

Страница 52: ......

Страница 53: ......

Страница 54: ......

Страница 55: ......

Страница 56: ......

Страница 57: ......

Страница 58: ......