SN8P2711A

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 60

Version 0.1

6

6

6

INTERRUPT

6.1 OVERVIEW

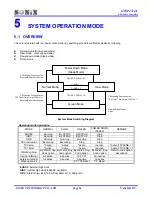

This MCU provides five interrupt sources, including three internal interrupt (TC0/TC1/ADC) and two external interrupt

(INT0/INT1). The external interrupt can wakeup the chip while the system is switched from power down mode to

high-speed normal mode, and interrupt request is latched until return to normal mode. Once interrupt service is

executed, the GIE bit in STKP register will clear to “0” for stopping other interrupt request. On the contrast, when

interrupt service exits, the GIE bit will set to “1” to accept the next interrupts’ request. All of the interrupt request signals

are stored in INTRQ register.

INTEN Interrupt Enable Register

Interrupt

Enable

Gating

INTRQ

5-Bit

Latchs

P00IRQ

P01IRQ

TC0IRQ

TC1IRQ

ADCIRQ

Interrupt Vector Address (0008H)

Global Interrupt Request Signal

INT0 Trigger

INT1 Trigger

TC0 Time Out

TC1 Time Out

ADC Converting Successfully

Note: The GIE bit must enable during all interrupt operation.