4 Signal description

02.05

© Siemens AG 1998 All Rights Reserved

4-2

FM-STEPDRIVE/SIMOSTEP (FB)

The signals and timing diagrams for the pulse and signal interfaces are

described in the following sections.

4.1 Pulse

interface

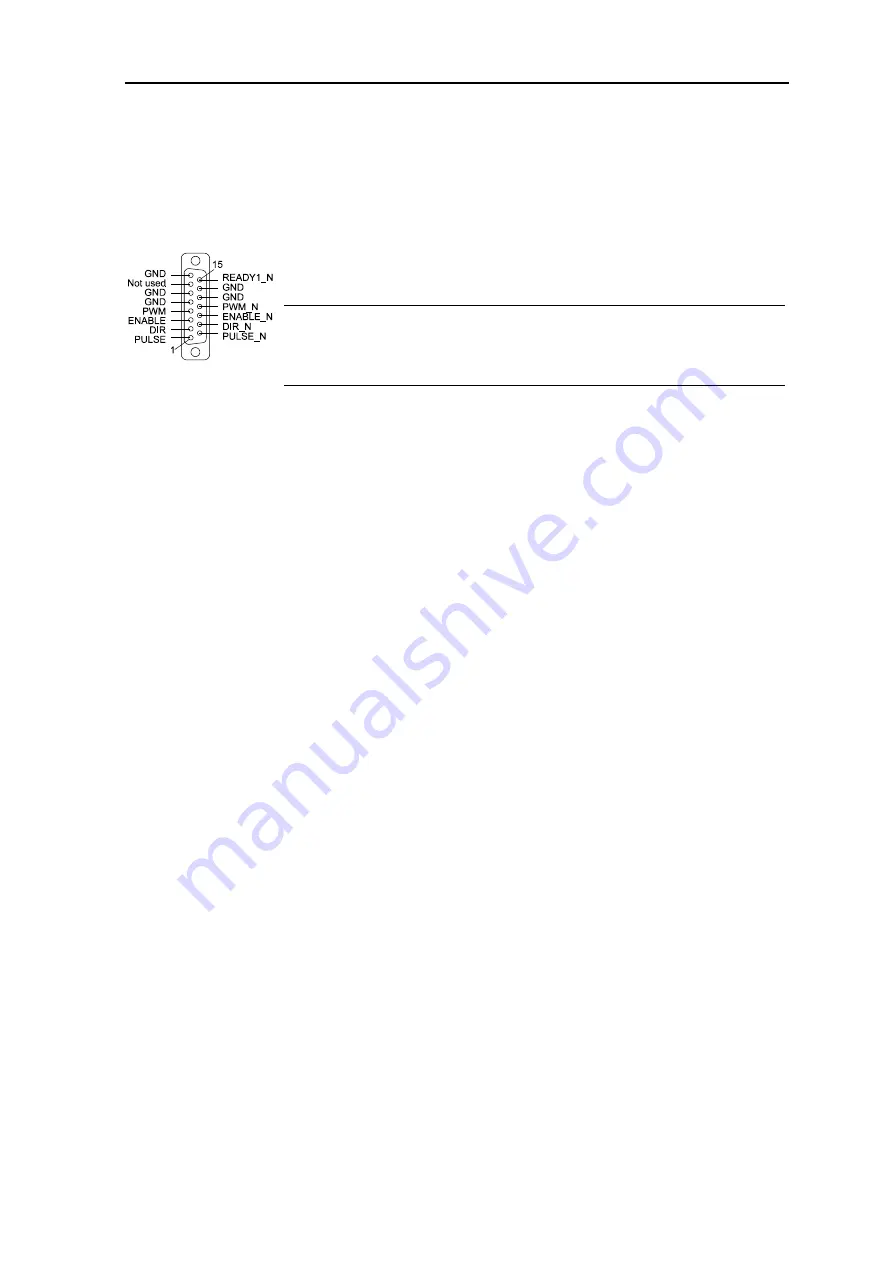

The pulse interface has four 5 V optocoupler inputs and one optocoupler

output.

Note

The technical data of the pulse interface are described in chapter 3.

The signal timing of the inputs/outputs is described in chapter 4.3.

Inputs:

PULSE (clock)

To start motor shaft rotation, rectangular clock pulses must be supplied to

the PULSE input. Each positive pulse edge triggers one motor step if the

power controller is in ready status and the GATE_N input is energized

(24 V).

The sense of rotation is preset with the direction input (DIR).

DIR (sense of rotation)

When the DIR signal input is deenergized, the motor turns in a clockwise

direction (as seen from front towards motor shaft). When this signal input

is energized, the motor turns in a counterclockwise direction (as seen

from front towards motor shaft). The sense of rotation can also be

inverted by interchanging two motor phase leads.

ENABLE (enable)

When the ENABLE input is energized, the power controller is enabled.

After approx. 500 ms, the power controller reports readiness via the

READY1_N and READY2 outputs and the motor is energized. If 24 V are

present at the GATE_N input of the signal interface, clock pulses can be

supplied to the PULSE input.

PWM (current control)

The set motor phase current can be modified using a pulse width

modulation signal on the PWM input in the range from 0% to 100%

(frequency range 10 kHz to 20 kHz). The phase current is determined by

the pulse/pause ratio of the PWM signal. If the signal input is

deenergized, the set phase current flows. If the signal input is energized,

the motor phase current is switched off. When the motor is stopped, it

does not have any holding torque.

Output:

READY1_N (readiness)

When the ENABLE input is activated, the power controller reports readiness

via the READY1_N output. When the power controller is ready, the

READY1_N output has low resistance. If 24 V are present at the GATE_N

input of the signal interface, clock pulses can be supplied to the PULSE

input.

In case of a power controller fault, or if a power controller enable signal

has not been received via the ENABLE input, the READY1_N output has

high resistance.

Содержание 1FL3041-0AC31-0BJ0

Страница 2: ......

Страница 6: ...II ...

Страница 8: ...IV ...

Страница 9: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 1 1 Overview 1 ...

Страница 11: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 2 1 Functional description 2 ...

Страница 14: ...2 Functional description 02 05 Siemens AG 1998 All Rights Reserved 2 4 FM STEPDRIVE SIMOSTEP FB ...

Страница 25: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 5 1 Mounting 5 ...

Страница 39: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 7 1 Setup 7 ...

Страница 41: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 8 1 Status indicators and troubleshooting 8 ...

Страница 44: ...8 Status indicators and troubleshooting 02 05 Siemens AG 1998 All Rights Reserved 8 4 FM STEPDRIVE SIMOSTEP FB ...

Страница 45: ... Siemens AG 1998 All Rights Reserved FM STEPDRIVE SIMOSTEP FB 9 1 SIMOSTEP specifications 9 ...

Страница 58: ......

Страница 59: ......