SM-SX1/SX1W

– 38 –

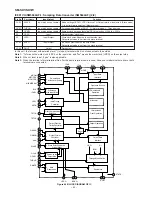

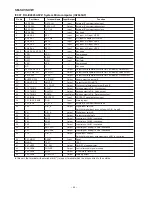

Figure 38 BLOCK DIAGRAM OF IC

SEL

PLL

EIAJ(AES/EBU)

Digital Audio

Interface Decoder

Microcomputer Interface

Data Clock

Control

S/P

P/S

Asynchronous

Buffer

(1 word per

each of

L and R)

System Clock

Timing Generator

EXTW

DDIN

CSM

ERR

EMP

FS1,0

CCK,CLD

CDO

DAUX

DIM1,0

HDLT

DOM1,0

DOUT

VFL

TST2

TSTN

RSTN

MCA,MCB,MCC,

WC,SYNC,OPT

KM0

VDDA

VSSA

PCO

CTLP,CTLN

LR

LOCKN

P256

KM2

XI

XO

KM1

SKSY

VDD

VSS

36

37

35

40

41

43 44

42

1

18 19

2

20 21

3

4

17

30

23

5

10

~

16

39

11

22

13

12

31

14

15

38

25 28

26

29

24

32

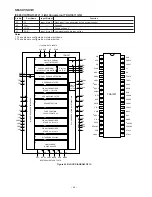

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

33

32

31

30

29

28

27

26

25

24

23

44

43

42

41

40

39

38

37

36

35

34

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCKN

VSS

TST2

DIM1

DIM0

DOM1

DOM0

KM1

FS1

KM0

KM2

TSTN

VSSA

CTLP

(NC)

PCO

CTLN

VDDA

RSTN

CLD

CCK

CDO

EMP

ERR

VDD

LR

DDIN

EXTW

CSM

FS0

IC800 VHiYM3436D/-1: Digital Interface Receiver (YM3436D)